## **HV-CMOS**

Ivan Peric for ATLAS and CLIC HVCMOS R&D and Mu3e Collaborations

- Ideas:

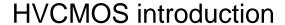

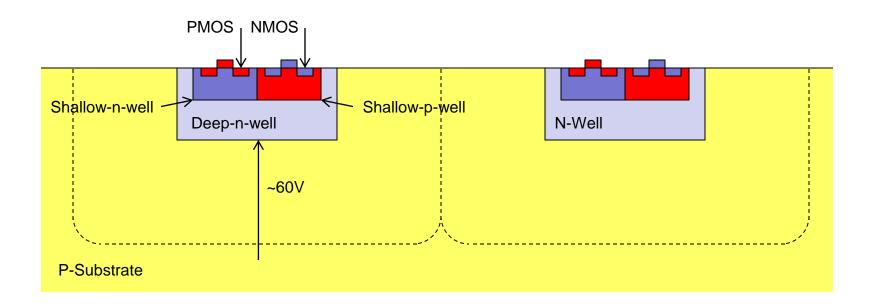

- Use the standard (HV)CMOS technologies to implement particle detectors

- Use a high voltage to deplete the sensor volume charge collection by drift

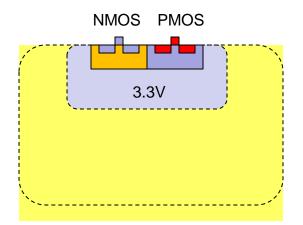

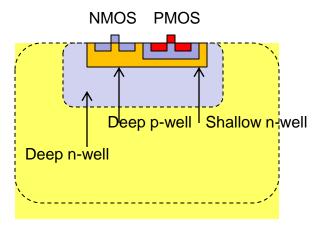

- The standard implementation: CMOS electronics inside the deep n-well-collecting electrode

- "Smart diode"

- Partial depletion from the top, no backside electrode needed

- Some drawbacks:

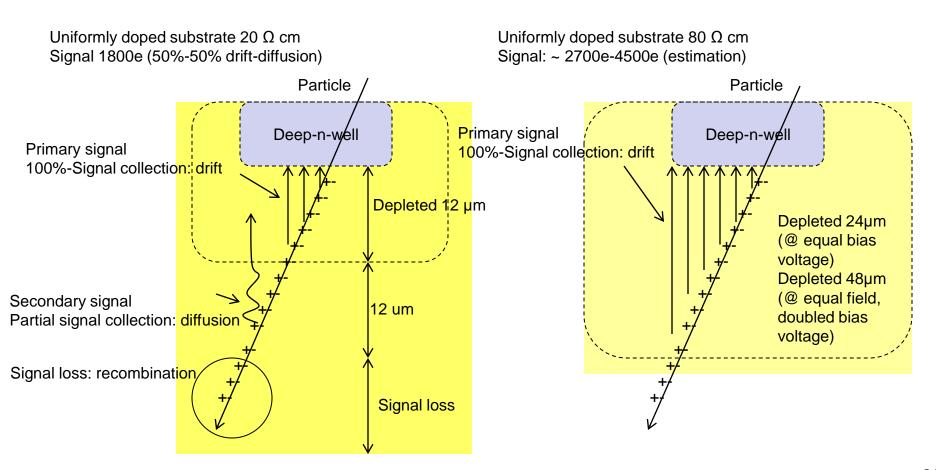

- The standard substrates are relatively low resistive ( $\sim$ 20  $\Omega$ cm)

- The depleted region is up to ~15 μm thick MIP signals are relatively weak ~ 1800 e

- The collection electrode is, at the same time, the PMOS bulk there is a strong capacitive crosstalk from PMOS transistors to the detector input.

- General drawback of monolithic sensors: Complex in-pixel electronics leads to increased detector capacitance or to decreased electrode-/pixel-size ratio

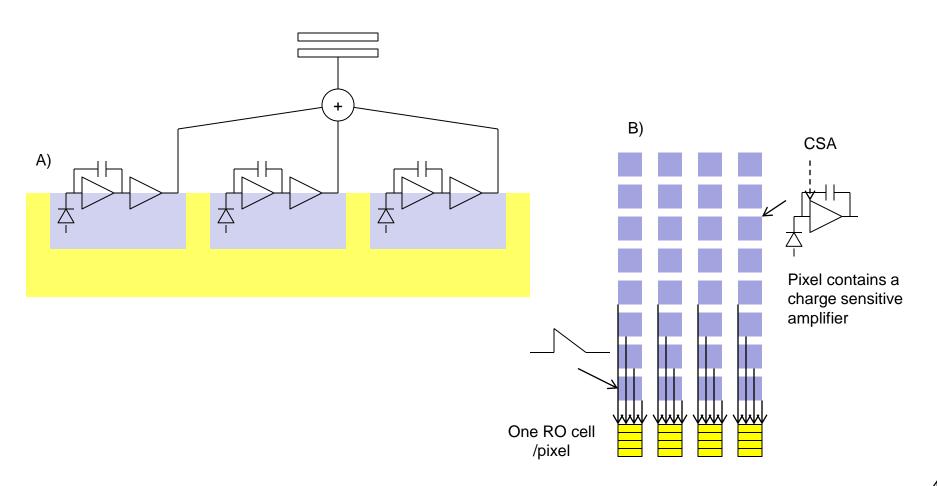

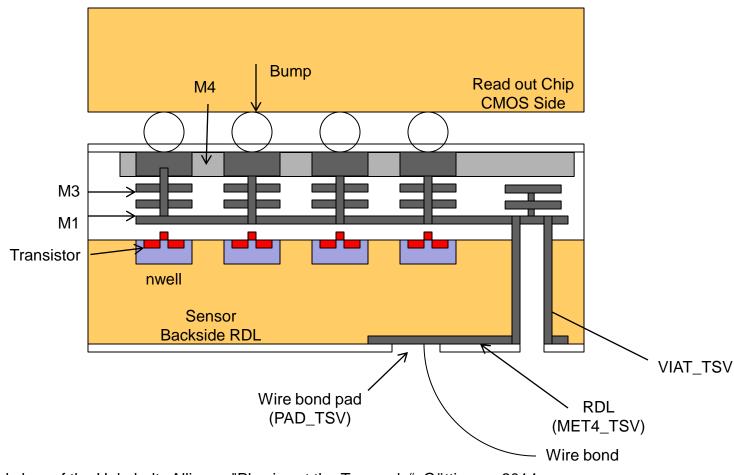

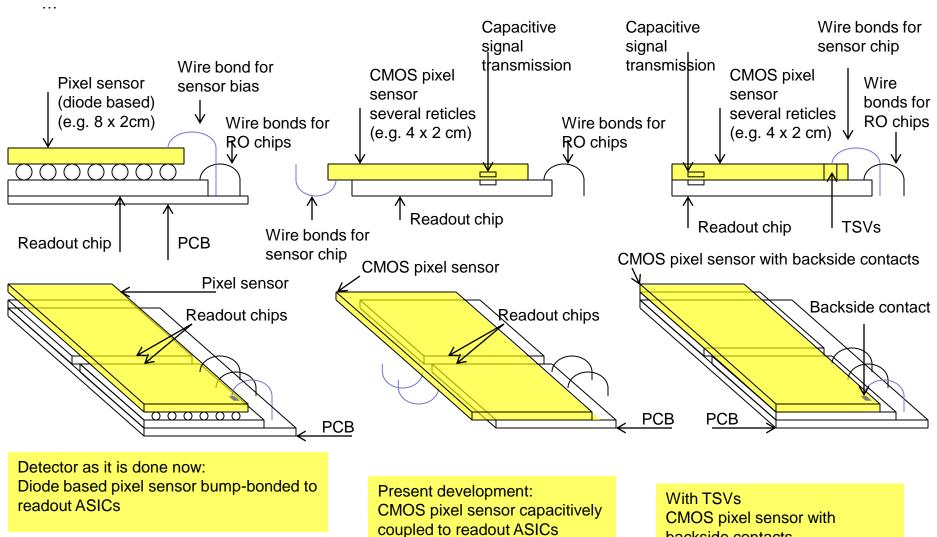

- We investigate two detector structures:

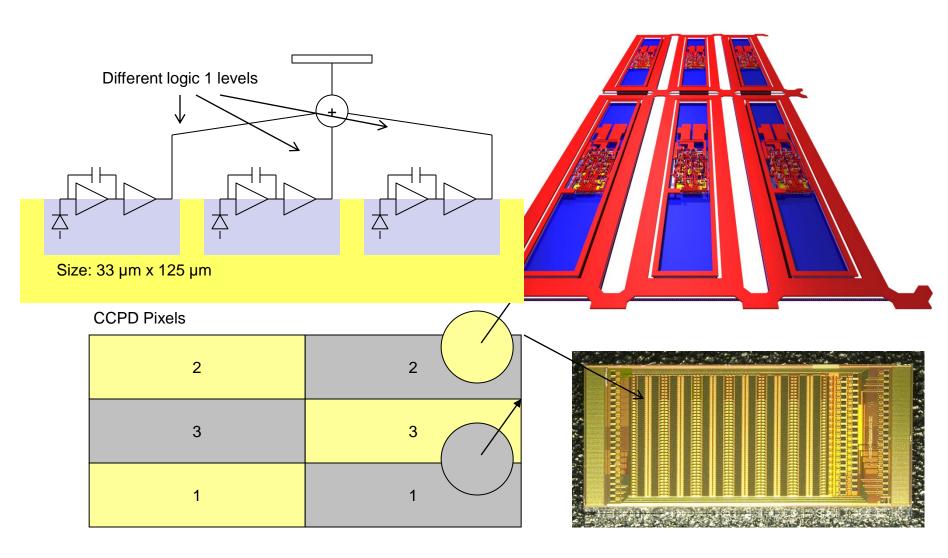

- A) Hybrid detector with a "smart" HVCMOS sensor and the capacitive signal transmission to the readout ASIC (capacitively coupled pixel sensor - CCPD)

- B) Monolithic pixel detector with digital signal processing on the chip periphery

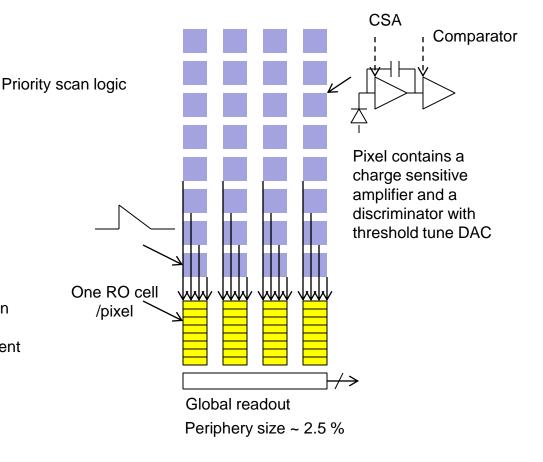

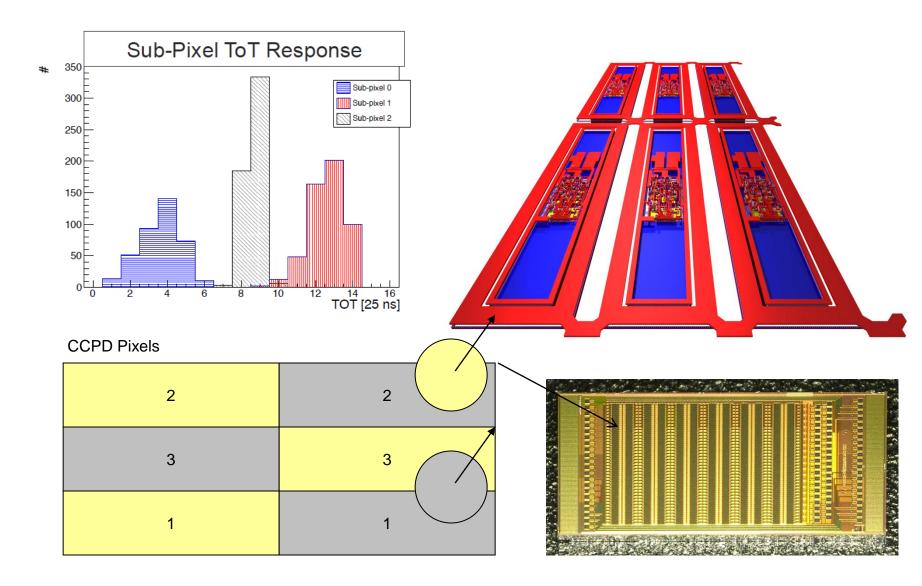

- CCPD

- ATLAS-pixel "style": the digital outputs of three pixels are multiplexed to one pixel readout cell

- HVCMOS pixel contains an amplifier and a comparator

- CLIC "style": every HVCMOS pixel has its own readout cell

- HVCMOS pixel contains only an amplifier

Size: 25 µm x 25 µm Readout pixel Size: 25 µm x 25 µm

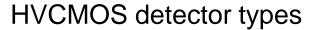

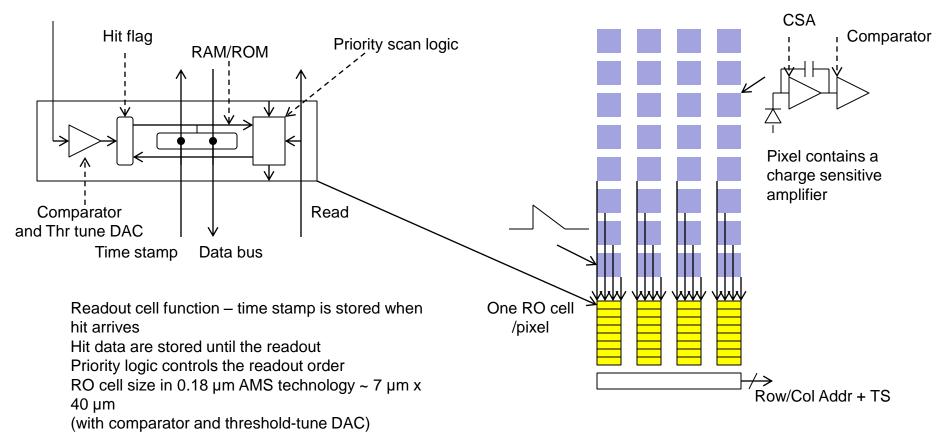

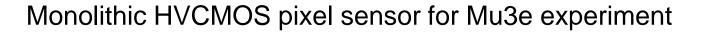

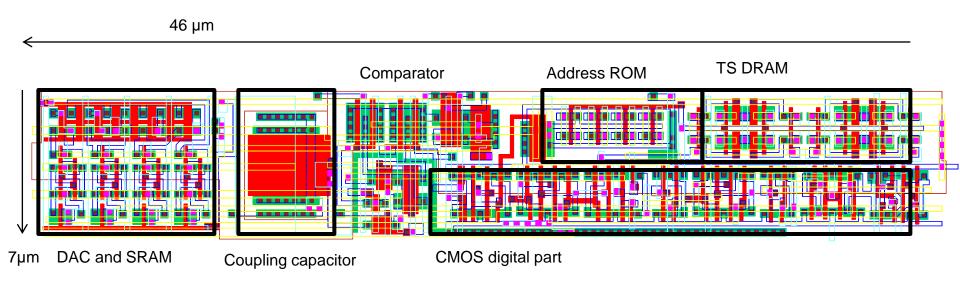

Monolithic HVCMOS pixel sensor for Mu3e experiment

## Monolithic HVCMOS pixel sensor for Mu3e experiment

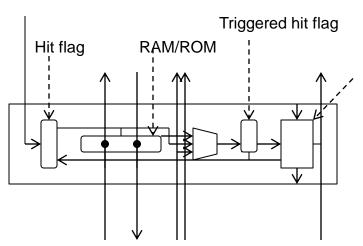

Concept: Every pixel has its own readout cell, placed on the chip periphery

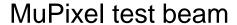

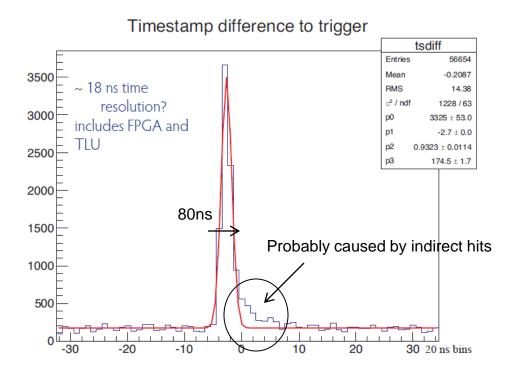

- Test-beam measurement February 2014 DESY

- Performed by our colleagues from Institute for Physics in Heidelberg

- Result analysis: Moritz Kiehn, Niklaus Berger, et al.

- Test-beam measurement February 2014 DESY

- Performed by our colleagues from Institute for Physics in Heidelberg

- Result analysis: Moritz Kiehn, Niklaus Berger, et al.

### Periphery area estimation for triggered readout

Concept: Every pixel has its own readout cell, placed on the chip periphery

Time stamp Delayed TS and trigger Read Data bus

Readout cell function – time stamp is stored when hit arrives

The stored time stamp is compared with the current time stamp

If trigger arrives with the correct latency, the triggered hit flag is set

Priority logic controls the readout order

Estimated cell size in 0.18 µm AMS technology

without comparator ~ 7 μm x 50 μm

Example: Pixel size 50 µm x 250 µm

Chip size: ~ 2 cm x 2 cm Number of pixels: 400 x 80

Size of periphery without comparator:

2 cm x 560 µm (~ 2.5%)

## **HVCMOS** pixel sensor for ATLAS

## CCPD detector (HV2FEI4)

The digital outputs of three pixels are multiplexed to one pixel readout cell

• "Sub-pixel resolution" by measuring of time over threshold (measurement: Malte Backhaus)

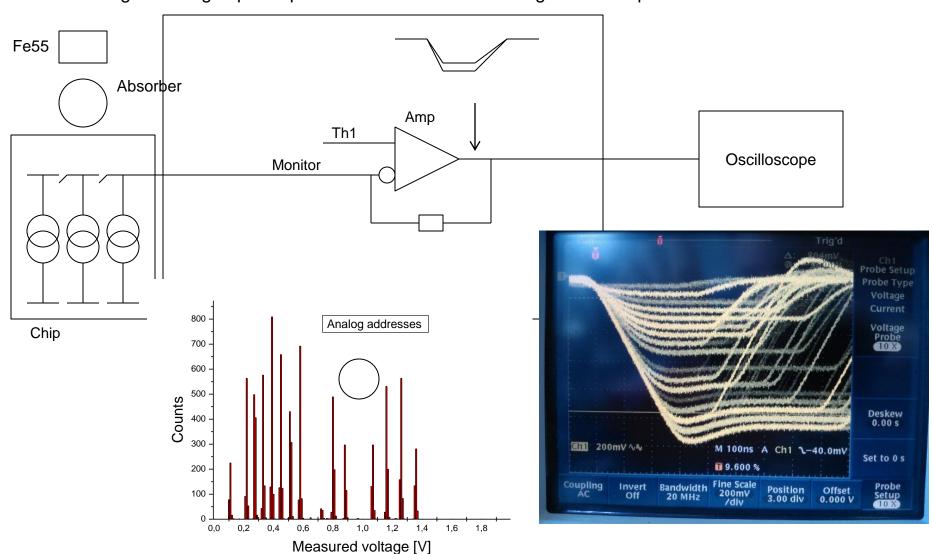

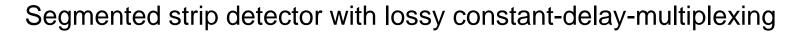

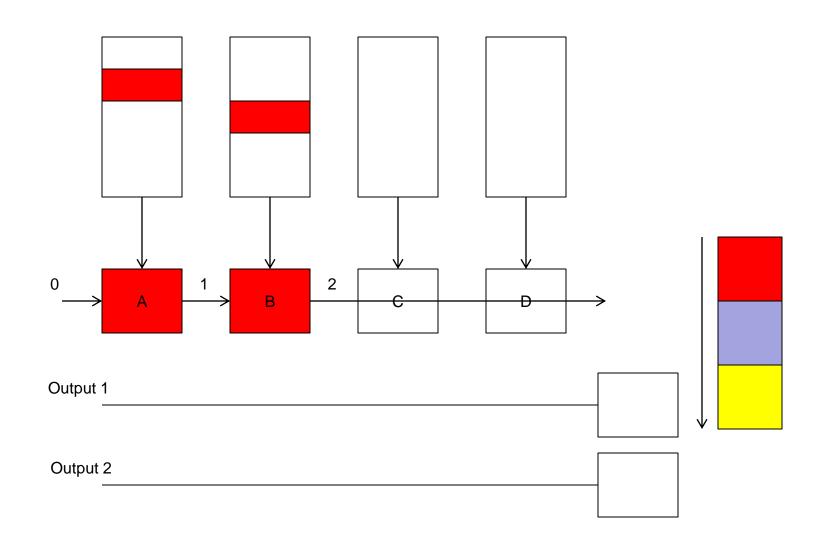

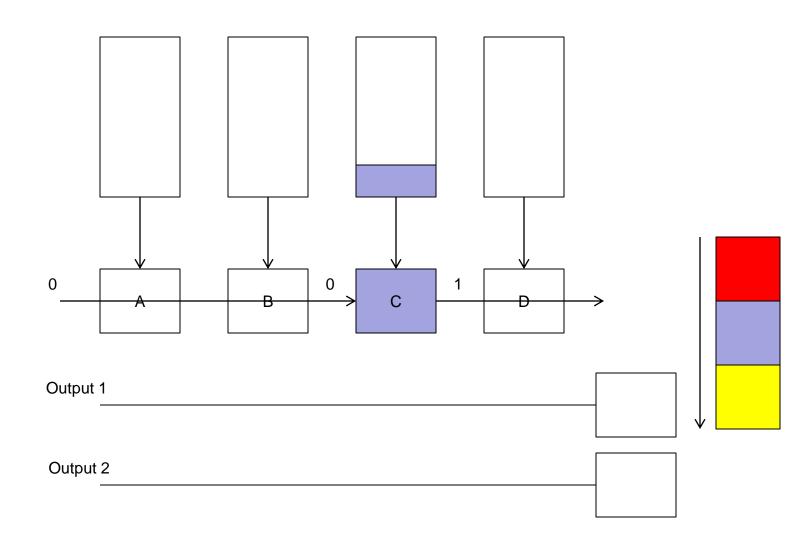

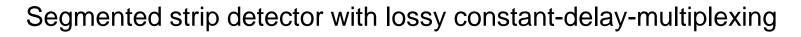

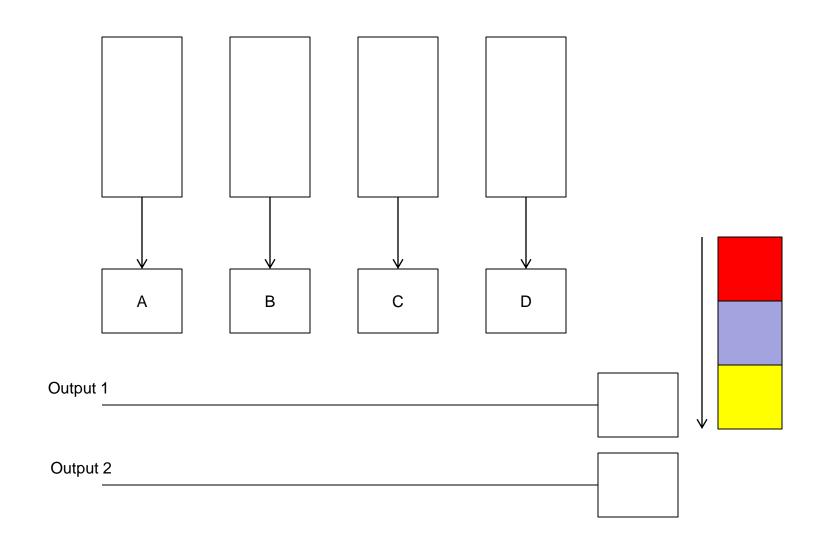

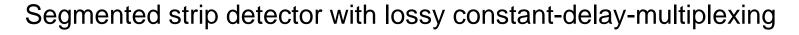

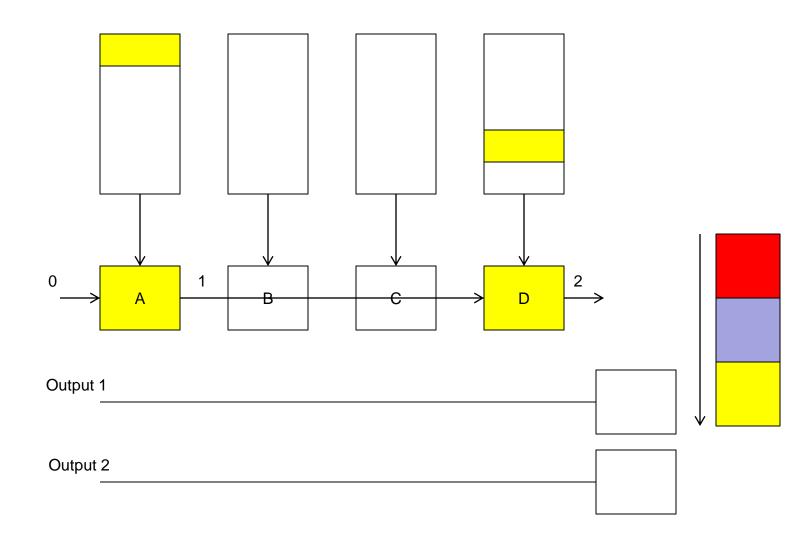

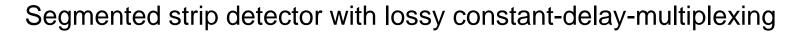

### HV2FEI4: segmented strip measurements

Analog encoding of pixels positions in the case of the segmented strip readout

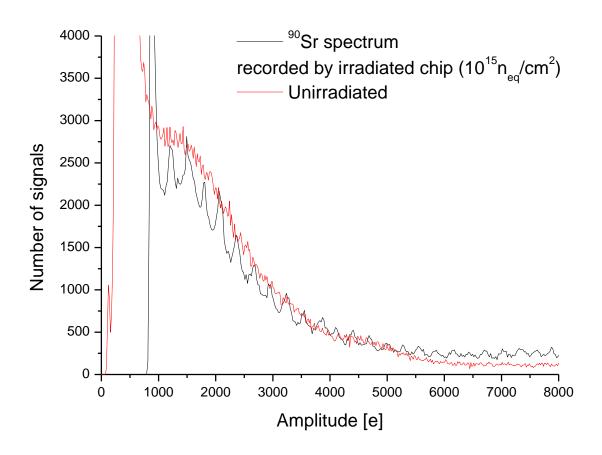

No evidence of signal decrease after 10<sup>15</sup> n<sub>eq</sub>/cm<sub>2</sub>

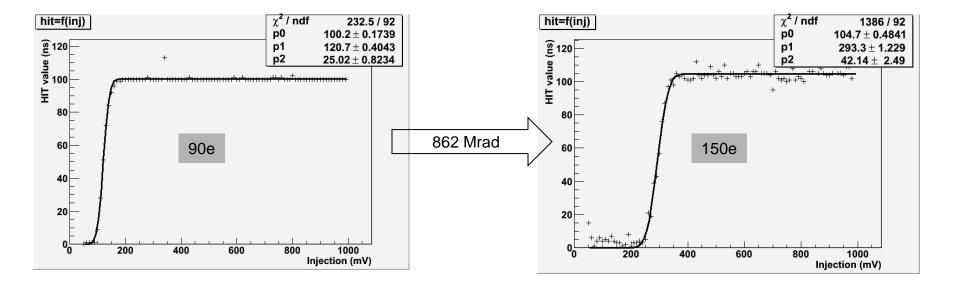

## HV2FEI4: x-ray irradiation to 862 Mrad

• A detector has been irradiated to 862 Mrad with x-rays. (chips on during the irradiation, 2 hours of annealing at 70C after each 100Mrad)

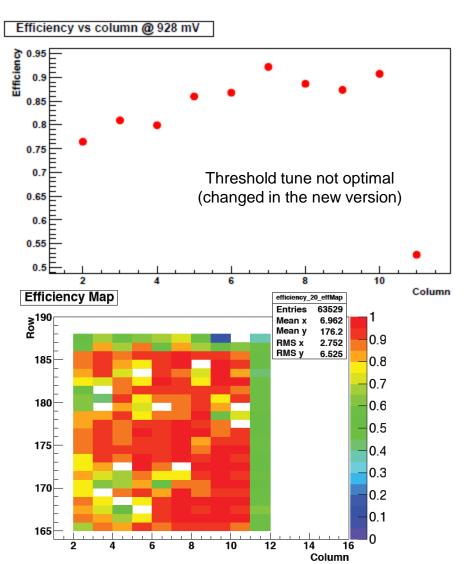

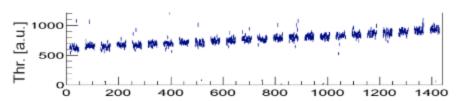

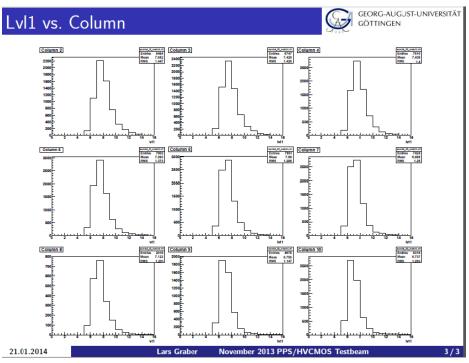

Test beam DESY, analysis: Lars Graber, et al.

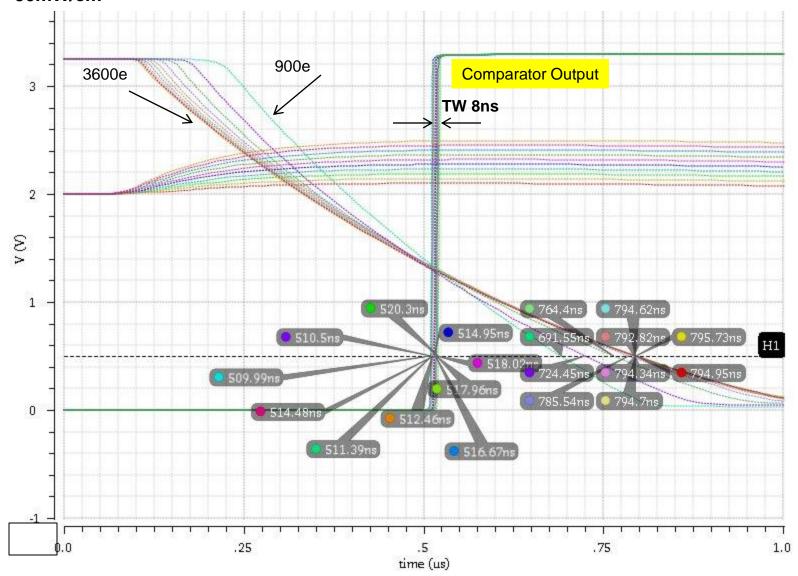

- We need to improve time walk

- We need to improve SNR of CCPDs for ATLAS, especially after irradiation

- Three strategies:

- 1) optimize present design

- 2) invent more clever electronics

- 3) improve the detector structure and technology

## Detector structure improvements

- Detector structure improvements:

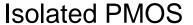

- Isolated PMOS

- Eliminates PMOS to sensor crosstalk, allows more freedom when pixel electronics is designed

#### Improvement:

- Detector structure improvements:

- High resistive substrates

- Detector structure improvements:

- High resistive substrates

- These improvements are possible within AMS- and LFoundry processes

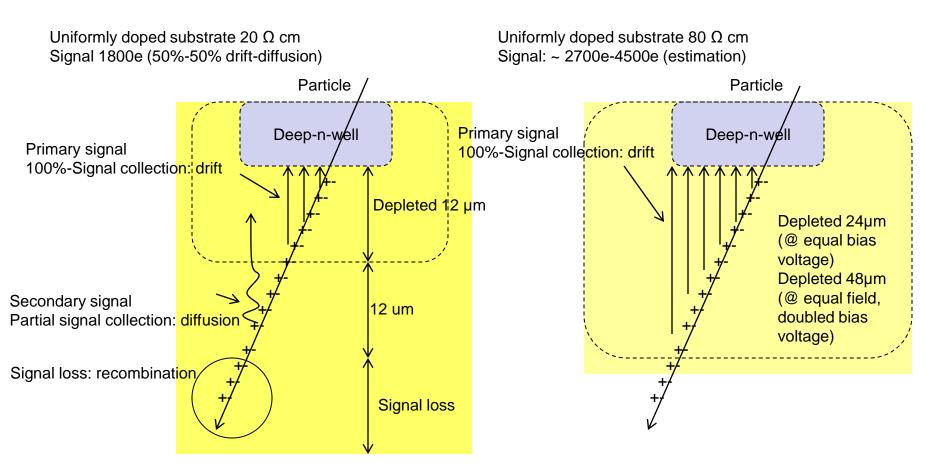

# AMS TSV process

- AMS offers through silicon vias and wafer bonding (so far only for H35, from end of 2015 for H18 as well)

- Backside redistribution layer and backside pads are possible

- TSV pitch 260 µm

- Very important for the module construction

#### Pixel detectors

backside contacts capacitively coupled to readout **ASICs**

## Summary

- Collaborations have been formed with the goals to develop HVCMOS sensors for ATLAS- and Mu3e experiments, as well for CLIC

- The Mu3e prototype detector (technology AMS 0.18 µm H18) (design Heidelberg) is a fully monolithic sensor with untriggered time-stamp based readout

- Detection efficiency of >99% has been measured in a beam test, time resolution (time walk) is ~

70 ns.

- The ATLAS prototypes in AMS 0.18 μm (H18) (design HD) and GF 0.13 μm (design CPPM, HD) technologies are capacitively coupled smart sensors that can be readout using FE-I4 chip

- Irradiations and test beam measurements have been performed on the H18 chip

- The H18-chip is operational after 880 MRad and 10<sup>16</sup> n<sub>ed</sub>/cm<sup>2</sup>

- A test beam measurement has been performed with the test-setups which are still not optimized and in development stage – the threshold uniformity was poor

- The uniradiated H18-detector had a detection efficiency of >90% in the regions with lower threshold

## Summary

- We need to improve the time walk and the detection efficiency

- Three approaches:

- 1) Optimization of the present design

- 2) Use of low-pass filter and the time-walk compensation circuit

- 3) Detector structure improvements (isolated PMOS) and the use of substrates of higher resistivity

- Chip producers AMS and LFoundry allow such "extra features" within their processes

- AMS additionally offers through silicon vias and wafer bonding (so far only for H35, from end of 2015 also for H18 process)

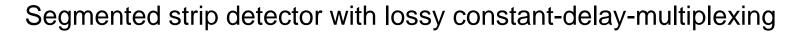

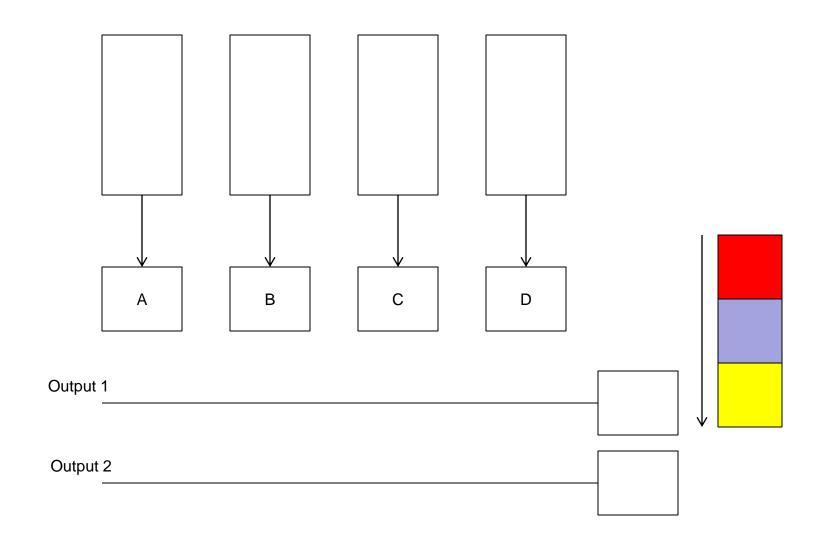

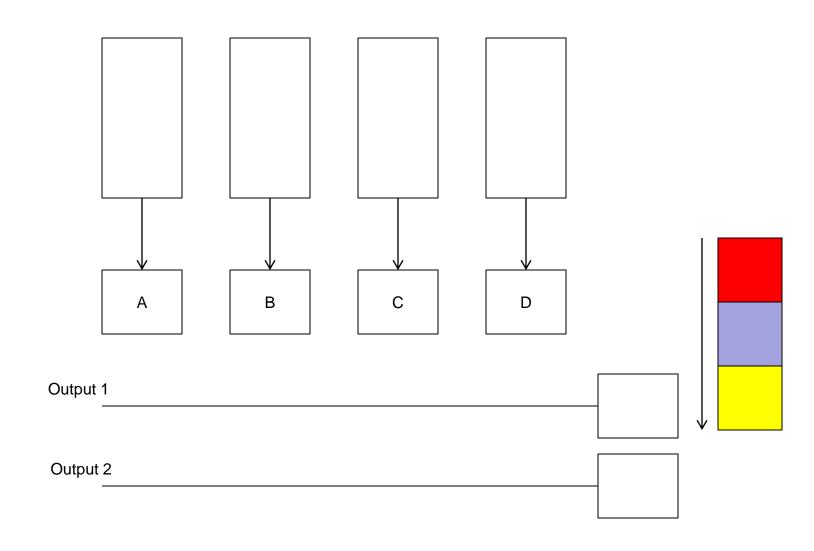

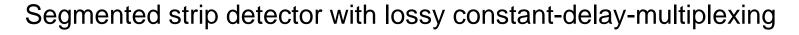

- We are also investigating the use of HVCMOS sensors (segmented strips) for the ATLAS strip layers

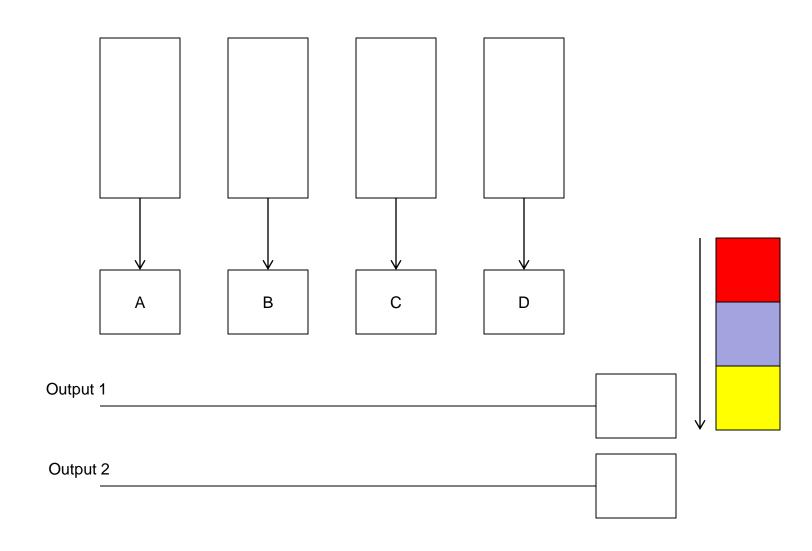

- Constant delay lossy multiplexing can be used every hit is transmitted to one of n outputs with a constant delay of ~60 ns.

- Hit loss occurs only if there are more than n simultaneous hits within one bunch crossing

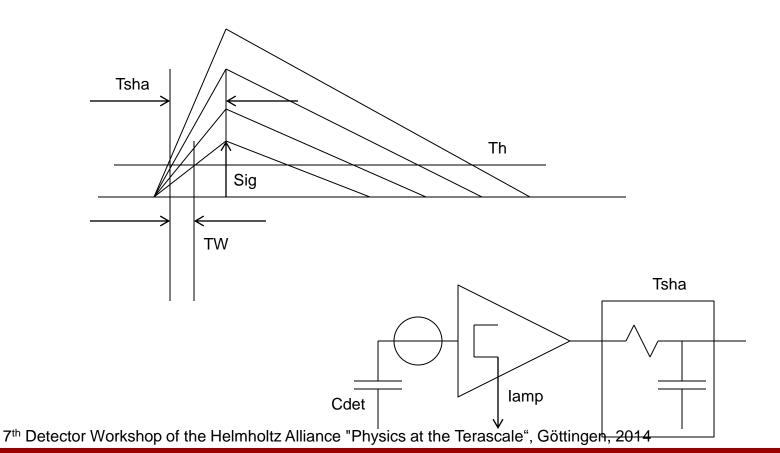

- The idea: Adding of low-pass filter decreases the noise without increasing the power consumption

- => Better SNR, lower threshold

- However: a slow output signal leads to a time-walk

- Time walk is caused 1) by the fluctuations of the input signal and 2) by the low and signaldependent response speed of the electronics

- Can we compensate for time walk, without decreasing the shaping time constants?

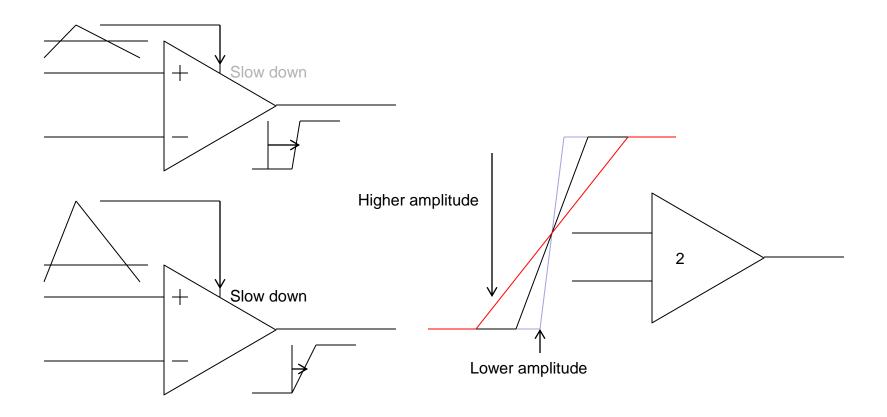

- Imagine a comparator which has the output zero-to-one transition speed, that depends on the input signal "overdrive"

- High amplitude signal faster threshold crossing but slower 0-1 transition

- Low amplitude signal slower threshold crossing but faster 0-1 transition

- Result: the threshold-crossing- and the transition time skews compensate each other

- Second comparator generates time-walk free signal

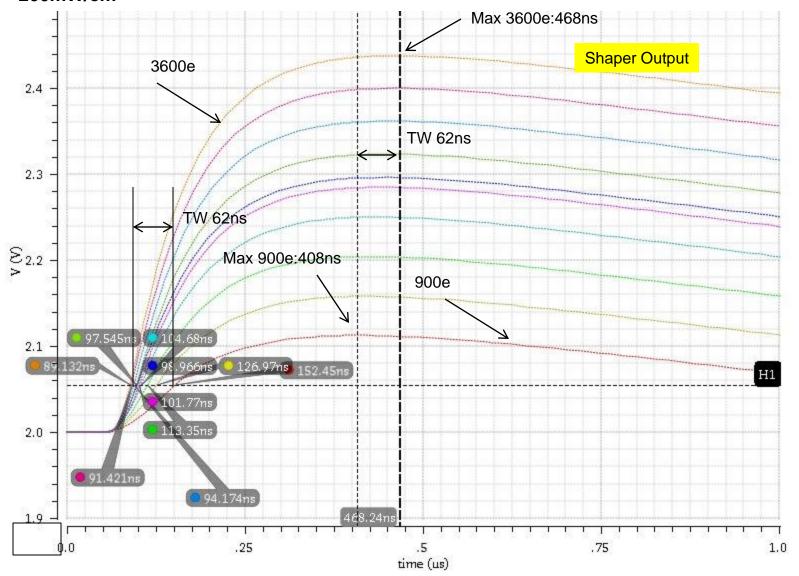

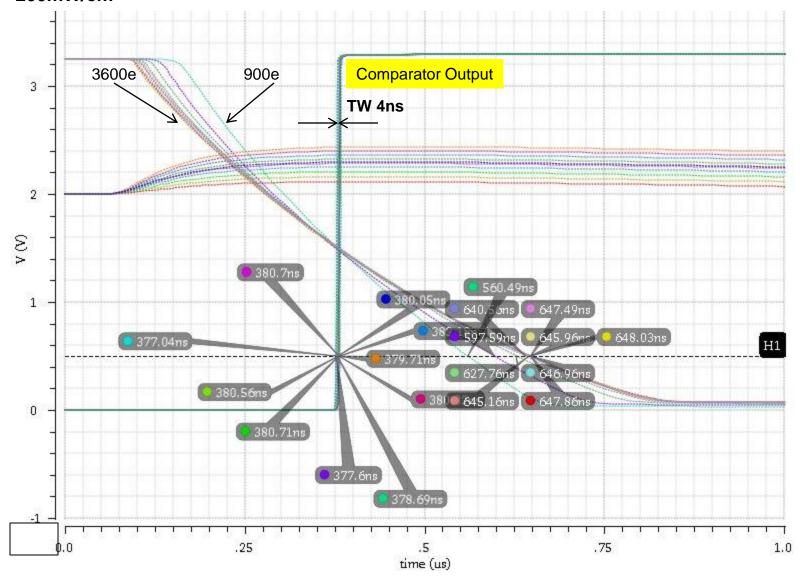

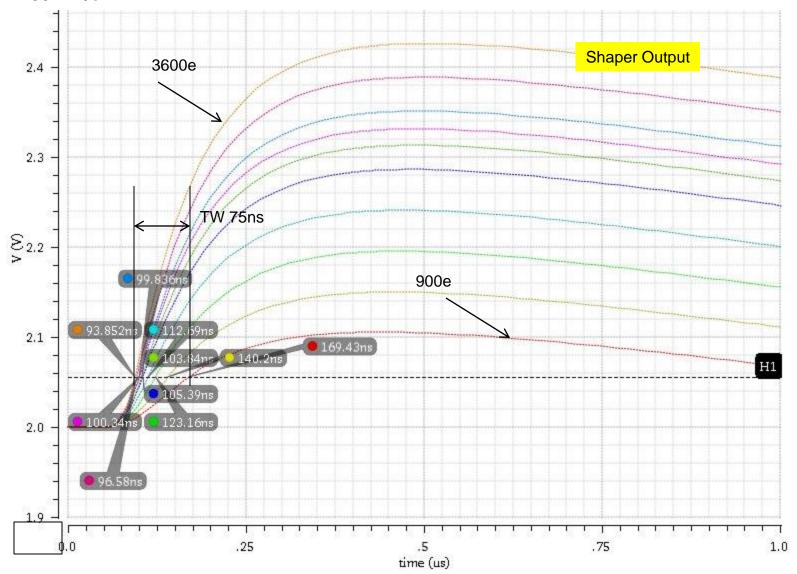

## Time Walk Compensation – AMS 350 nm

Noise=8.8mV, Thr=55mV, Bias current=10µA, Pixel size = 50x250µm, Ifoll=10, amplifier power

200mW/cm<sup>2</sup>

## Time Walk Compensation – AMS 350 nm

Noise=8.8mV, Thr=55mV, Bias current=10µA, Pixel size = 50x250µm, Ifoll=10, amplifier power

200mW/cm<sup>2</sup>

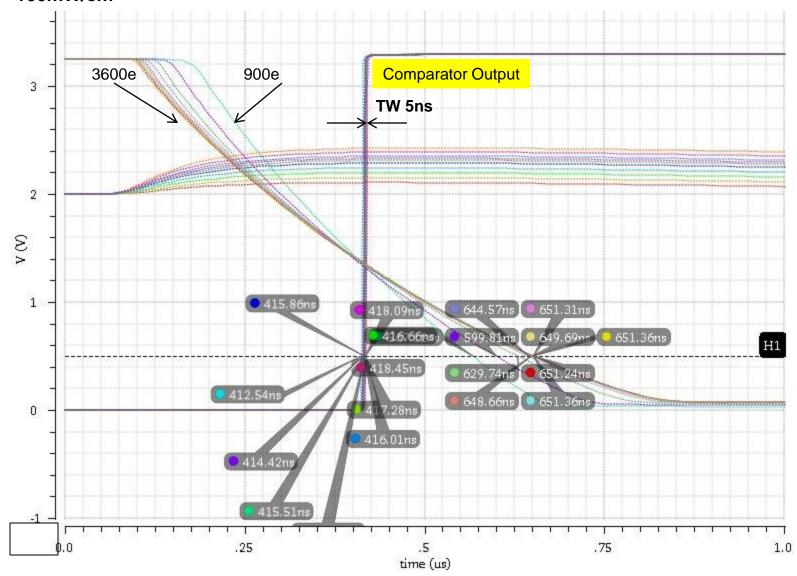

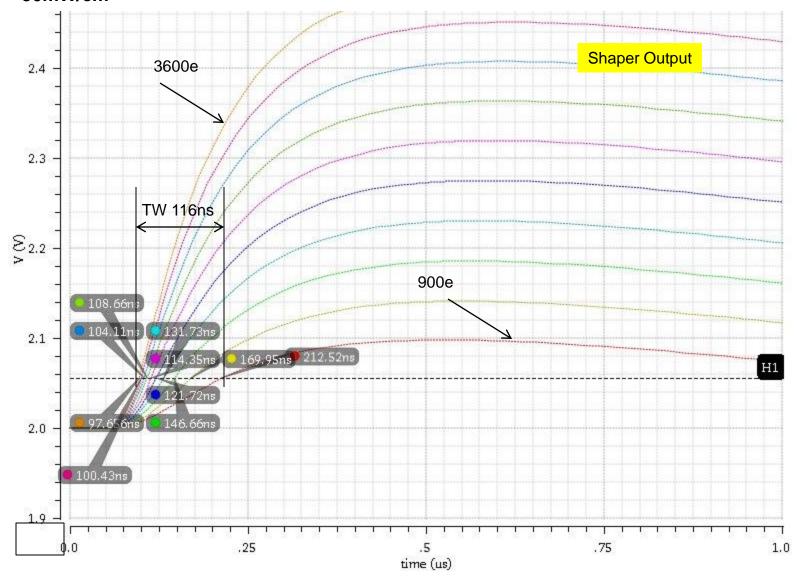

Noise=8.0mV, Thr=55mV, Bias current=10µA, Pixel size = 50x500µm, Ifoll=7, amplifier power

100mW/cm²

Noise=8.0mV, Thr=55mV, Bias current=10μA, Pixel size = 50x500μm, Ifoll=7, amplifier power

100mW/cm<sup>2</sup>

Noise=7.9mV, Thr=55mV, Bias current=5μA, Pixel size = 50x500μm, Ifoll=5, amplifier power

50mW/cm<sup>2</sup>

Noise=7.9mV, Thr=55mV, Bias current=5μA, Pixel size = 50x500μm, Ifoll=5, amplifier power

50mW/cm<sup>2</sup>