Stefan Ritt, Paul Scherrer Institute, Switzerland

Luca Galli, Fabio Morsani, Donato Nicolò, INFN Pisa, Italy

#### THE WaveDAQ SYSTEM FOR THE MEG II UPGRADE

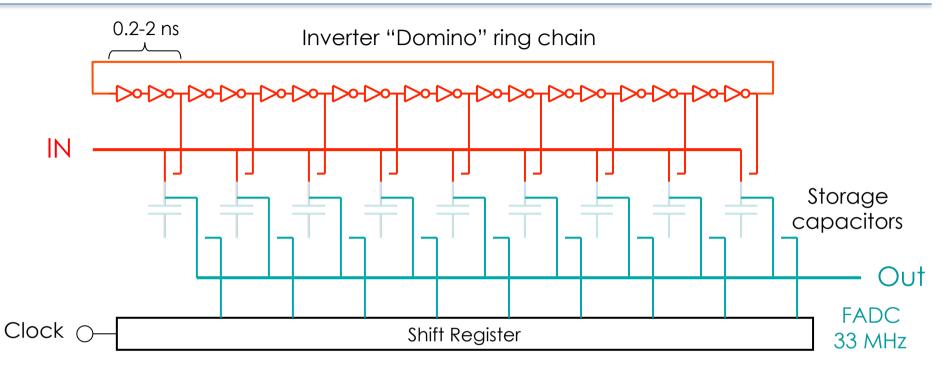

# DRS4 Chip

- Switched Capacitor Array (Analog Memory) developed at PSI

- 5 GSPS / 11.5 bits SNR, 9 channels on 5 mm x 5 mm chip, 40 mW / chn.

- Used at ~200 locations worldwide

- 2012: "Gigahertz Waveform Sampling: An Overview and Outlook"

- Pile-up rejection O(~10 ns)

- Time measurement O(10 ps)

- Charge measurement O(0.1%)

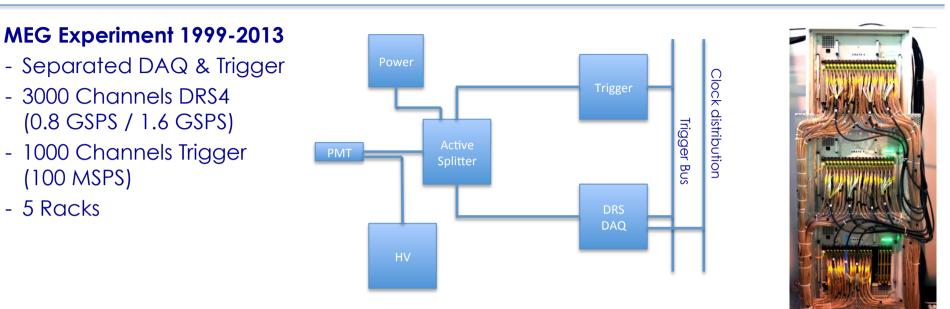

#### MEG & MEG II

#### MEG II Experiment 2014-

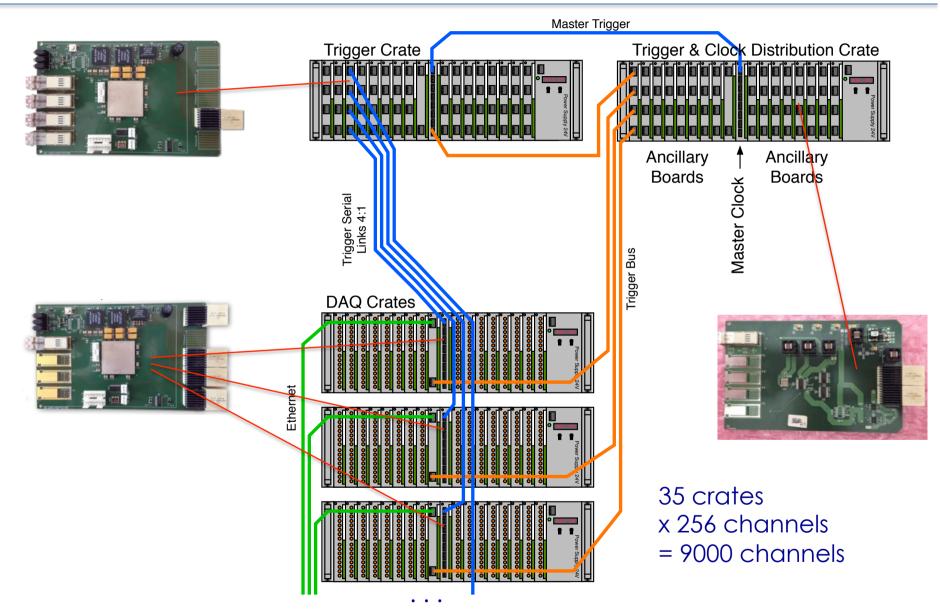

- 9000 Channels

- Same rack space

→Combine

DAQ & Trigger

S2: M. de Gerone: An extreme high resolution Timing Counter for the MEG II Experiment

S2P: M. Simonetta: Test and characterization of SiPMs intended as detector for the MEG timing counter

S5P: D. Nicolò: An FPGA-based trigger for the MEG II Experiment

S5P: A. Pepino: A high performance Front End Electronics for Drift Chamber readout in the MEG II Experiment

S7P: M. Grassi: A new cylindrical drift chamber for the MEG II Experiment

S7P: G. Rutar: A Dedicated Calibration Tool for the MEG and MEG II Positron Spectrometer

S7P: L. Galli: MEG II drift chamber prototype characterization with the silicon based cosmic ray tracker at INFN Pisa

S7P: M. Venturini: Ageing tests for the MEG II drift chamber

S9P: D. Nicolò: A liquid hydrogen target for the calibration of the MEG and MEG II liquid xenon calorimeter

S9P: K. leki: Upgrade of the MEG liquid xenon calorimeter with VUV-light sensitive large area SiPMs

### Crate Options

| VME      | ATCA     | ???                   |

|----------|----------|-----------------------|

| <b>v</b> | <b>v</b> | <b>v</b>              |

| ×        | <b>v</b> | <b>~</b>              |

| ×        | <b>v</b> | <ul> <li>✓</li> </ul> |

| ×        | ×        | <b>v</b>              |

| ×        | ×        | <b>v</b>              |

| ×        | ×        | <b>v</b>              |

| ×        | ×        | <ul> <li>✓</li> </ul> |

|          |          |                       |

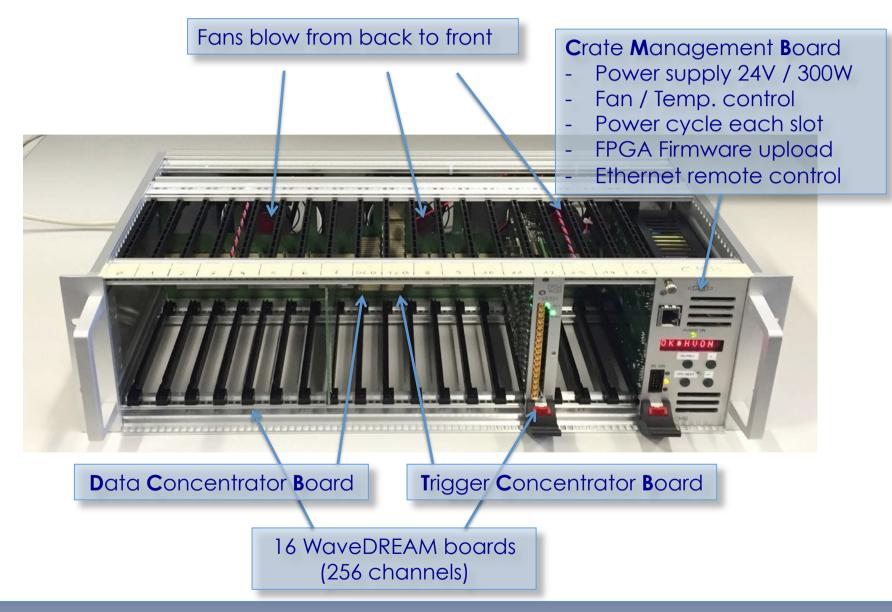

#### WaveDAQ System

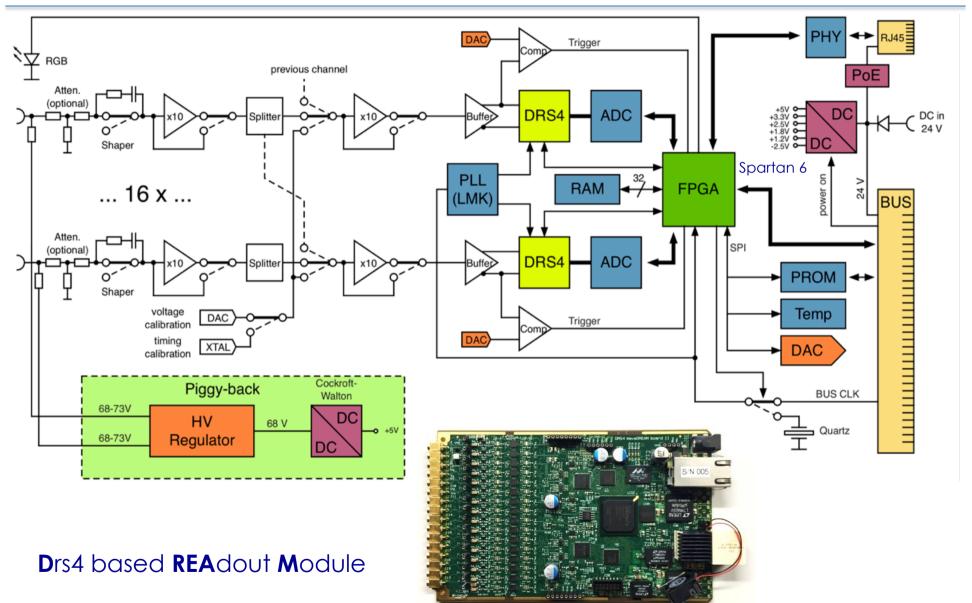

#### WaveDREAM Board (WDB)

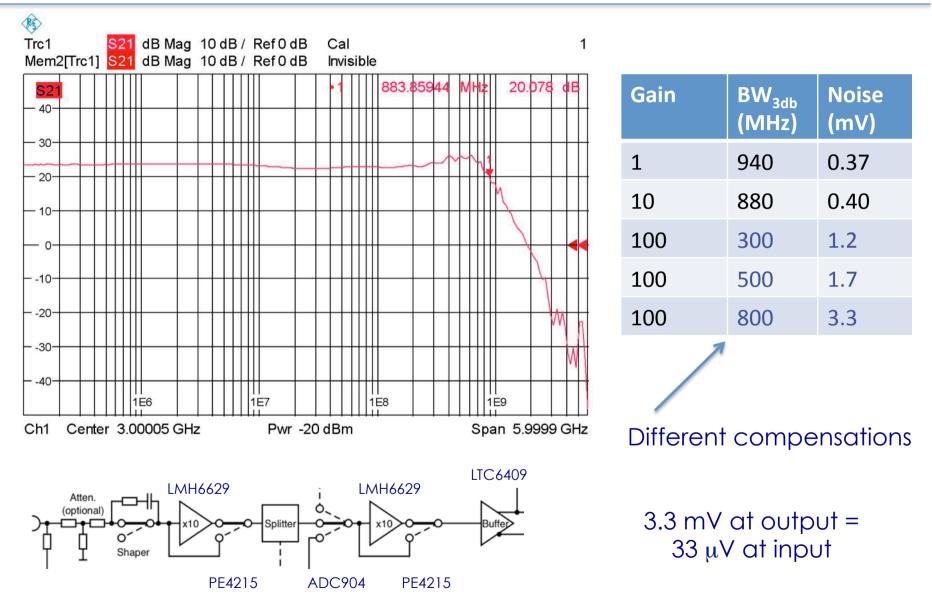

### Preamp

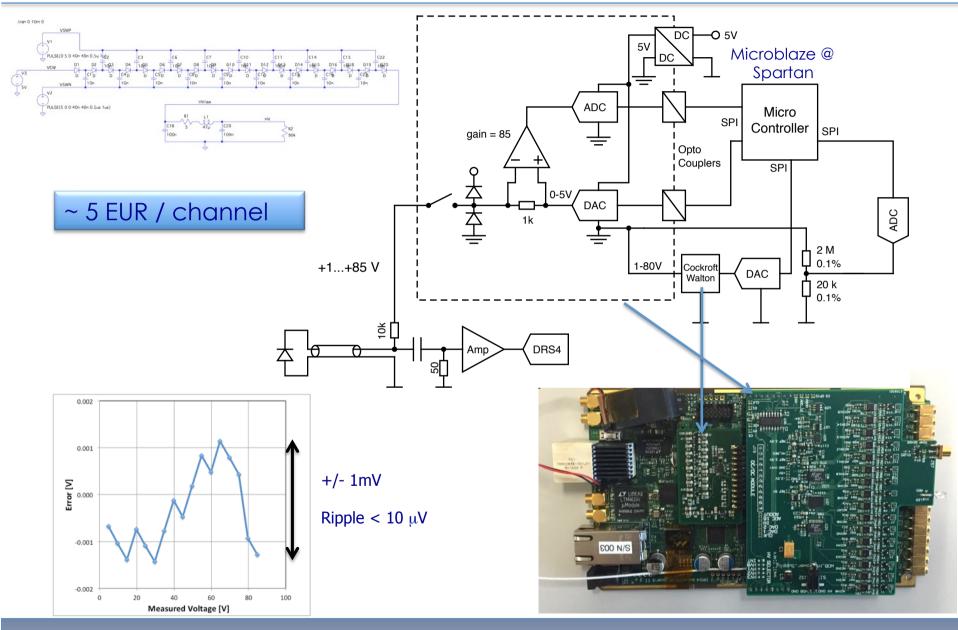

#### WaveDREAM2 HV

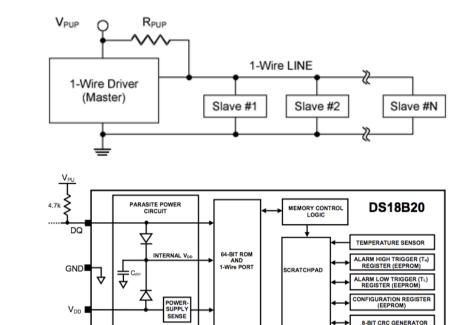

#### **Temperature Sensor Extension**

DS18B20

JNC

GND

□ N.C.

**Programmable Resolution**

**1-Wire Digital Thermometer**

User-Definable Nonvolatile (NV) Alarm

Alarm Search Command Identifies and

Software Compatible with the DS1822

Industrial Systems, Consumer Products,

Addresses Devices Whose Temperature is

Outside Programmed Limits (Temperature

Available in 8-Pin SO (150 mils), 8-Pin µSOP,

Applications Include Thermostatic Controls,

Thermometers, or Any Thermally Sensitive

N.C. [

N.C

DO

N.C. 🗆

SO (150 mils)

(DS18B20Z)

Settings

System

MAXIM

18B20

1 2 3

9 g a

.

Alarm Condition)

and 3-Pin TO-92 Packages

**PIN CONFIGURATIONS**

maxim integrated...

#### DESCRIPTION

The DS18B20 digital thermometer provides 9-bit to 12-bit Celsius temperature measurements and has an alarm function with nonvolatile userprogrammable upper and lower trigger points. The DS18B20 communicates over a 1-Wire bus that by definition requires only one data line (and ground) for communication with a central microprocessor. It has an operating temperature range of -55°C to +125°C and is accurate to ±0.5°C over the range of -10°C to +85°C. In addition, the DS18B20 can derive power directly from the data line ("parasite power"), eliminating the need for an external power supply.

Each DS18B20 has a unique 64-bit serial code, which allows multiple DS18B20s to function on the same 1-Wire bus. Thus, it is simple to use one microprocessor to control many DS18B20s distributed over a large area. Applications that can benefit from this feature include HVAC environmental controls, temperature monitoring systems inside buildings, equipment, or machinery, and process monitoring and control systems.

#### **FEATURES**

- Unique 1-Wire® Interface Requires Only One Port Pin for Communication Each Device has a Unique 64-Bit Serial Code

- 1-16 sensors per WD2 board with only one coaxial cable

- Automatic HV adjustments with temperature changes

28 May 2015

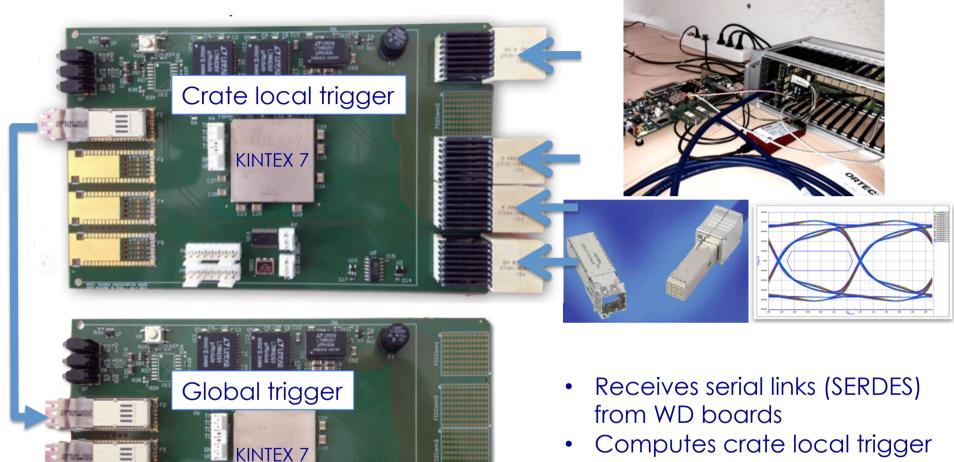

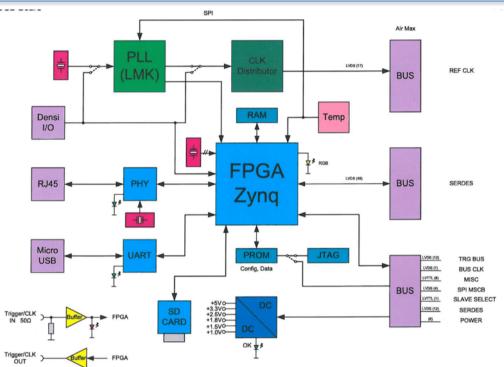

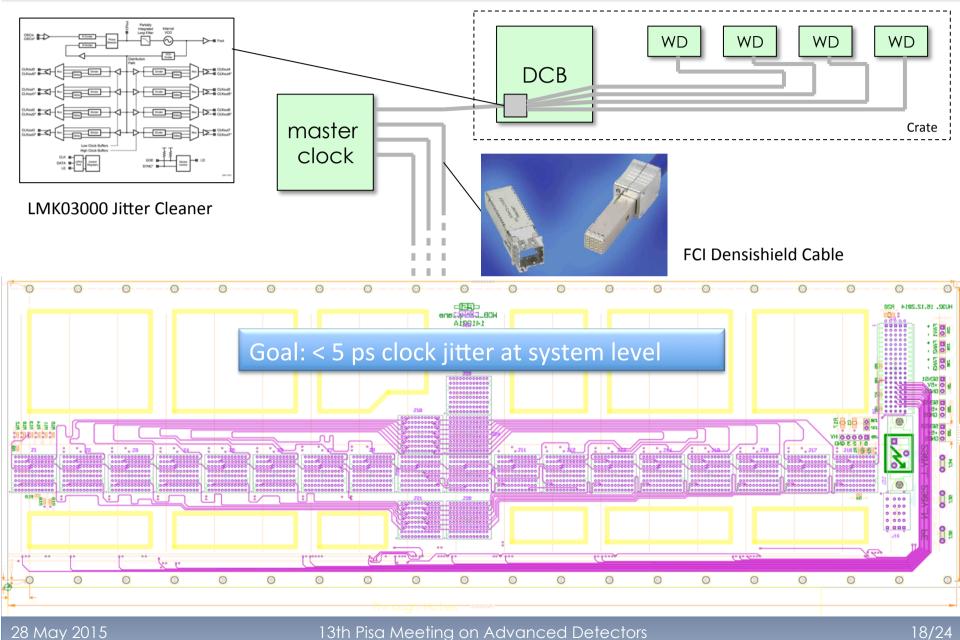

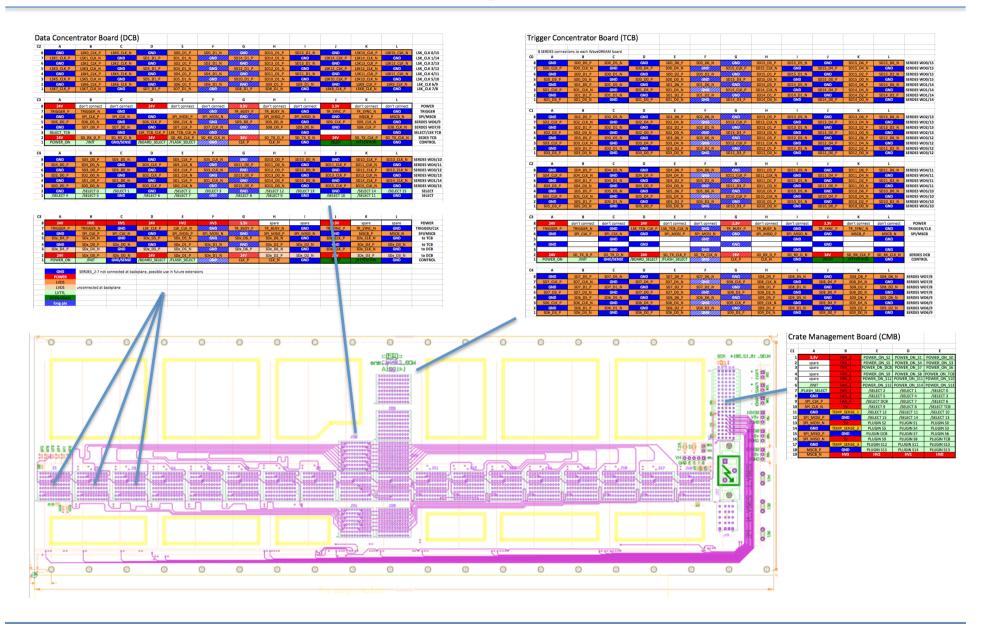

#### Trigger Concentrator Board (TCB)

- Send trigger via serial links to global trigger in dedicated crate

- FCI Densishield cables

#### Ancillary system

- Contains master clock

- Distribute clock (jitter < 12 ps measured)</li>

- Distribute trigger

- 4 diff. pairs for

- Clock

- Trigger

- Busy

- (Sync)

Spare (Sync)

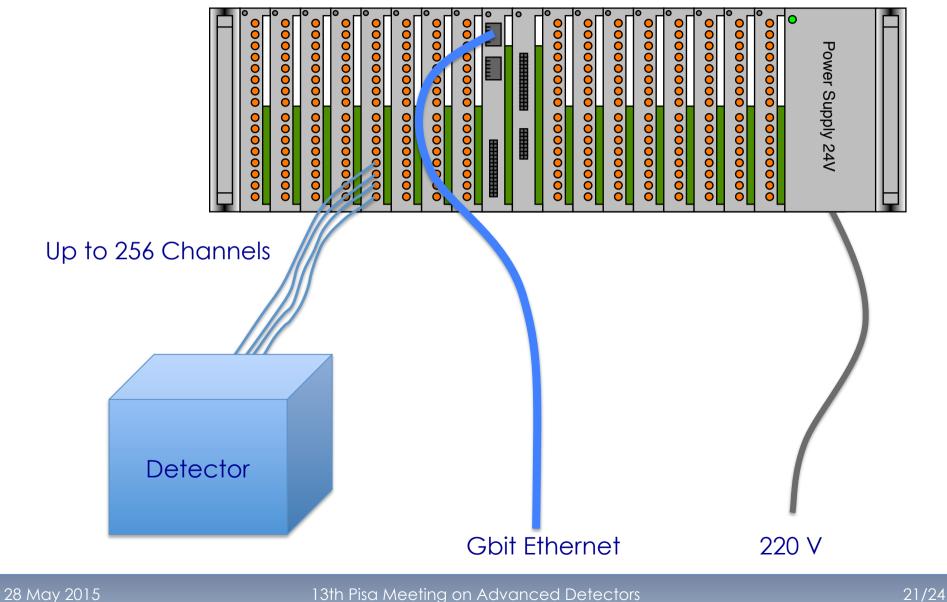

## DAQ Concentrator Board (DCB)

- Receive Gbit links from WDB

- Use SERDES instead GTX (lower latency)

- Waveform preprocessing in Zynq CPU

- Output via Gbit Ethernet (10 Gbit optional)

- Board under design

- Tests with Zed-Board and "Backplane Simulator"

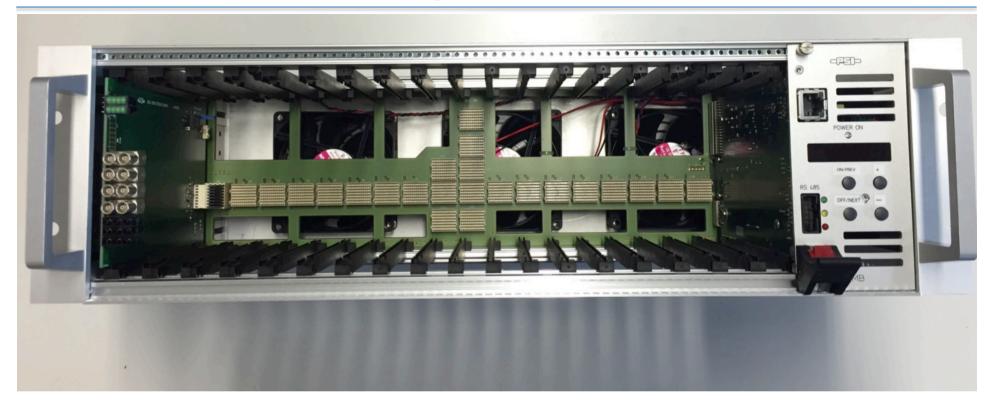

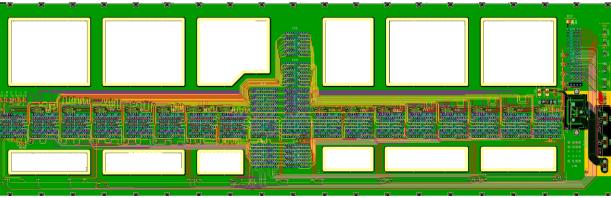

# Half Height Backplane

28 May 2015

13th Pisa Meeting on Advanced Detectors

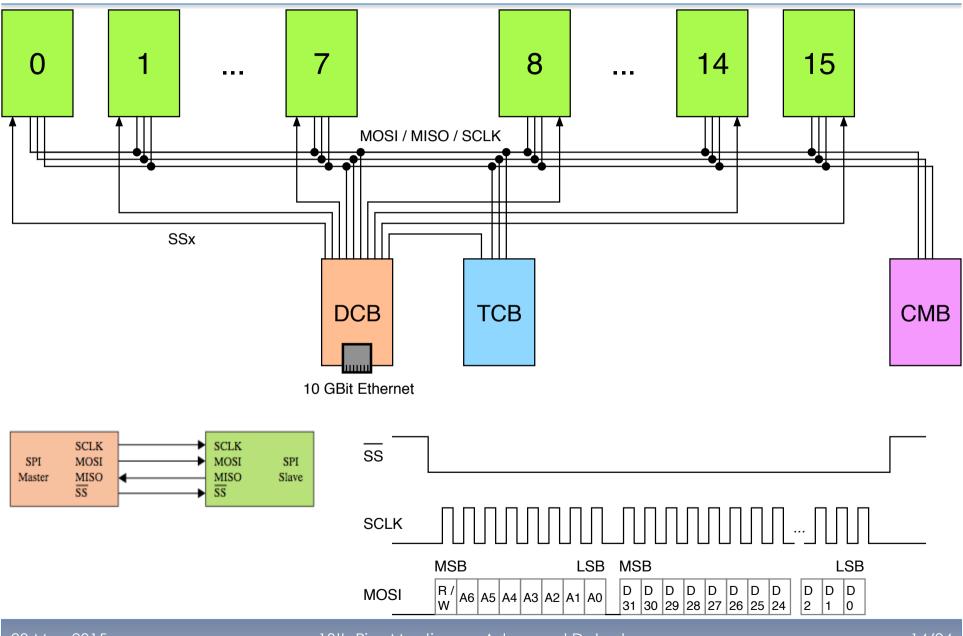

#### SPI configuration

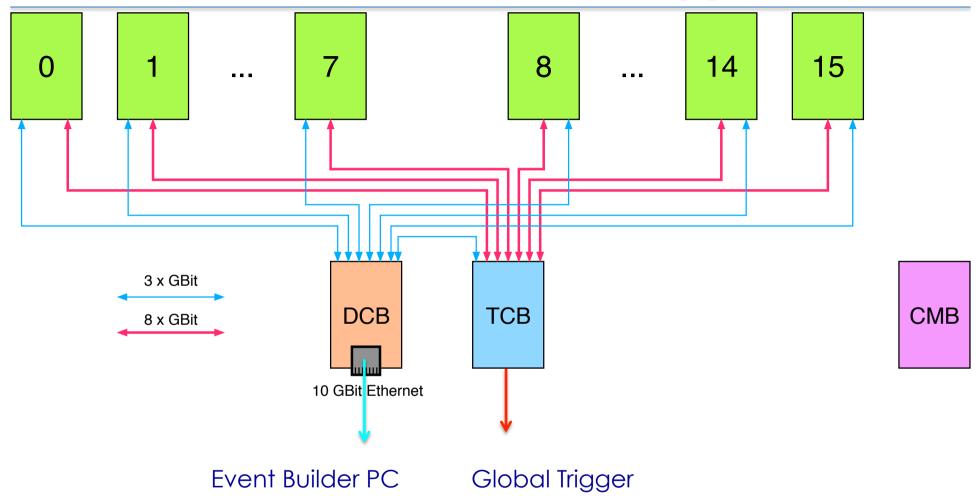

#### Gbit links for DAQ & Trigger

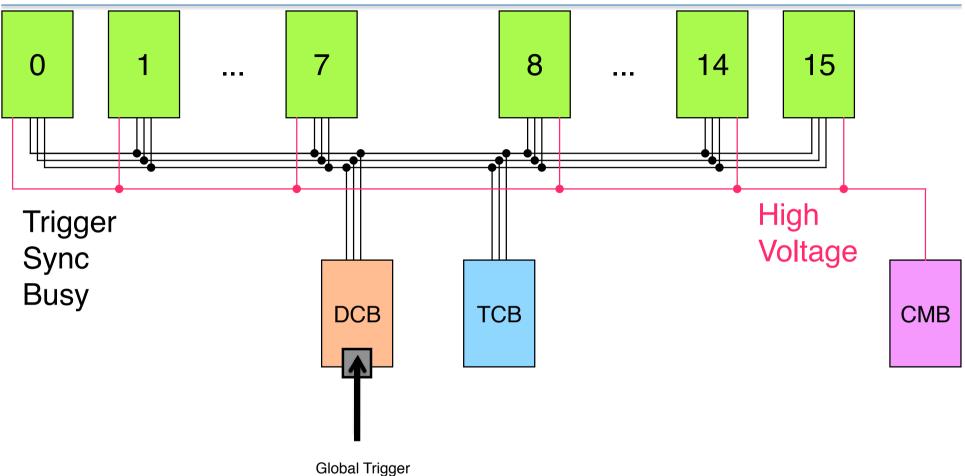

#### Trigger Bus & HV

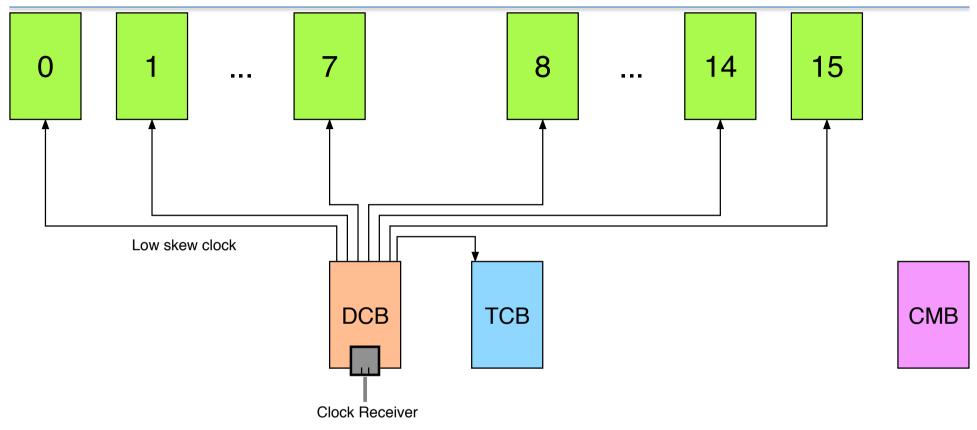

#### **Clock Distribution**

#### WaveDAQ Clock Distribution

#### Pin Assignment

#### Minimal System

#### One-crate system

## MEG II System

#### WaveDAQ Performance

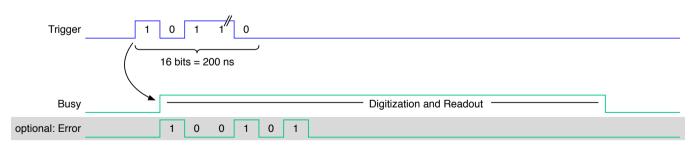

- Trigger resolution 10 ns (100 MHz clock)

- Trigger bandwidth 8 Gbit / s

- Trigger latency <380 ns \*) (9000 channels)</li>

- DAQ bandwidth 2 Gbit / s

- DAQ time measurement 10 ps \*)

- DAQ dead time 3 35  $\mu$ s / event

- MEG II: 7 x 10<sup>7</sup>  $\mu$ /s, DAQ eff. > 95% @ 30 Hz \*)

\*) projected

#### Conclusions

- WaveDAQ system has been designed to fulfill needs of MEG II experiment

- System has huge potential for many others (costs: ~130 EUR / channel)

- Status: Crate fully working, trigger board and WaveDREAM board successfully tested, firmware to be finished, DCB under design

- First full crate test end of 2015, full system (35 crates) in 2016

- DRS5 chip (no dead-time) planned for 2017+