# The MuPix 10 – the current state of design

Alena Weber for the Mu3e Collaboration

ASIC and Detector Laboratory, Karlsruhe Institute of Technology and University Heidelberg

#### **The Mu3e Experiment**

HighR UNIVERSITÄT SEIT 1386 Karlsruher Institut für Technolog

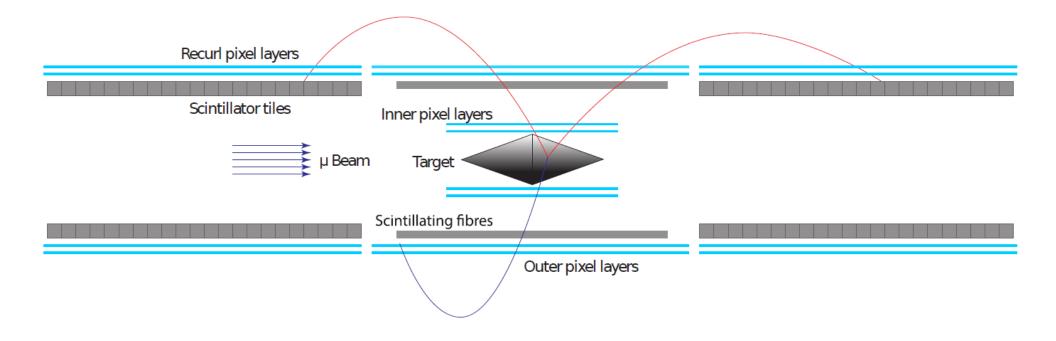

- Searching for  $\mu^+ \rightarrow e^+ e^- e^+$

- Main requirements of the detector:

- Precise tracking

- Minimal material budget

- High Voltage Monolithic Active Pixel Sensors (HV-MAPS) fulfil requirements

- Chosen for tracking layers

- $\rightarrow$  On track to the final chip

26.03.2019

2

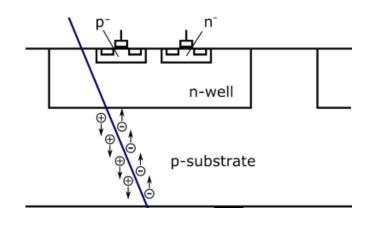

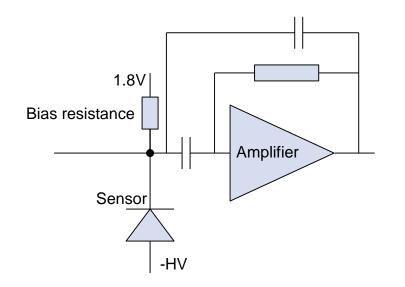

### **HVCMOS**

= High Voltage Complementary Metal Oxide Semiconductor

#### Features

- Fast and efficient charge collection by drift

- Sensor and electronics on the same die

→ monolithic

- Low cost

- Thinned to 50 μm

#### **Properties**

■ High depletion voltage ≈ -150 V

Highℝ ∖ ⁺++

- 30 µm depletion depth

- Standard process

UNIVERSITÄT HEIDELBERG ZUKUNFT SEIT 1386

Karleruhar Instit

# Overview of the latest MuPix and ATLASPix sensors

#### **Main Challenges**

#### Surrounding

- Full size: active sensor size ≈ 2 x 2 cm<sup>2</sup>

- Move to new technology

From AMS to TSI

- One single supply voltage

#### Aim

Provide a chip for building functional Mu3e modules

#### **Design Challenges**

- Fully functional

- Operate multiple chips on flexprint

- Limited routing possibilities on flexprint

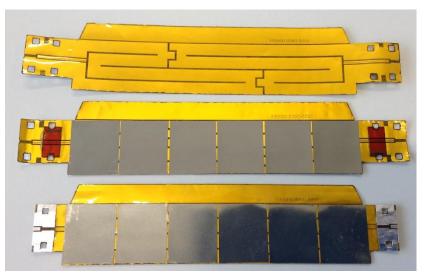

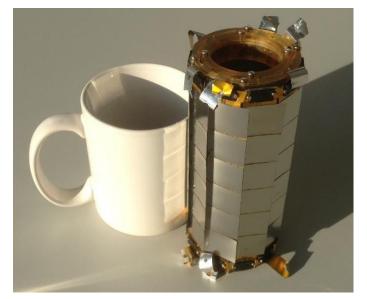

Parts of the existing mockup

#### Design transfer to another technology

#### AMS ah18

- Used for several prototypes > 10

- 6 metal layers

#### Chances

- One metal layer more: will be used for optimized routing

- Similar technology

#### TSI 180 nm HVCMOS

- First use in our group in 2018

- Submitted three chips

- Verification by comparison of MuPix7 in AMS and in TSI

Highℝ

7 metal layers

#### Challenges

- Layout has to be redone for a few circuits

- Design rules different from metal 5 to the top

- Process similar but not the same

6

UNIVERSITÄT HEIDELBERG ZUKUNFT

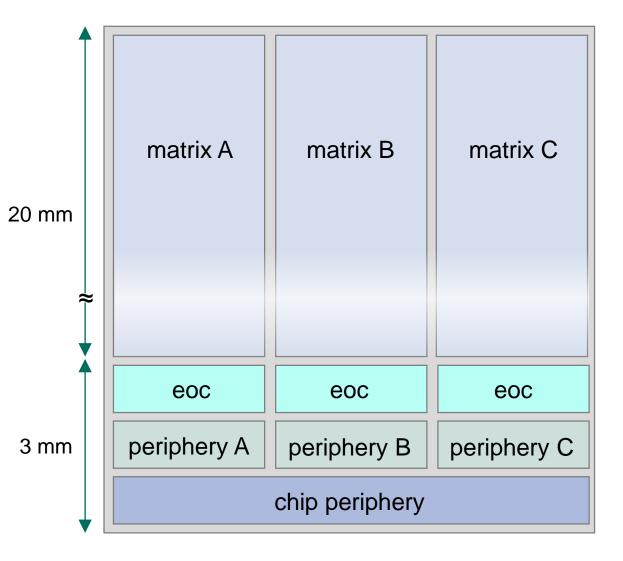

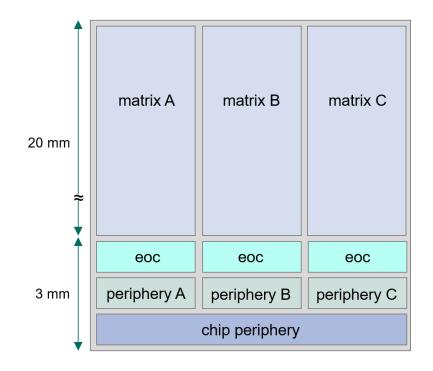

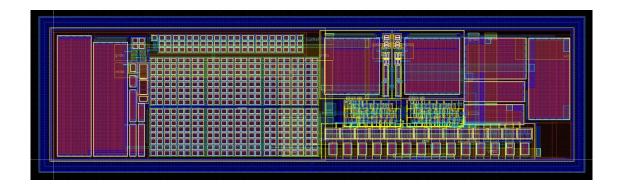

#### **Chip overview**

#### Main parts

- Pixel matrix divided in three submatrices

- Pixel periphery with end of column (eoc)

- Submatrix periphery

- Chip periphery

7

#### **Matrix Design – three submatrices**

#### **Common features**

- Pixel size 80 x 80 μm<sup>2</sup>

- 250 pixels per column, in total 250 columns

- Same state machine but one for every matrix

- Chip periphery

#### Challenges

Operate all matrices at the same time with corresponding configuration and shared chip periphery

#### Separated parts and differences

- Configuration bits can be set individually

- Pixel amplifiers

- Signal transmission

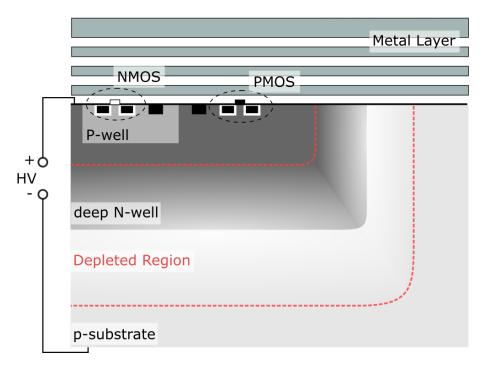

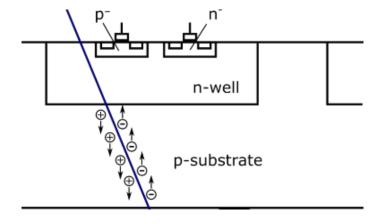

#### **Pixel Cell - Diode**

#### **Properties**

- Pixel size 80 x 80 μm<sup>2</sup>

- Diode formed by the deep n-well and p-substrate

- New geometry of n-well

#### Optimization

- Geometry of charge collection diode will be optimized with TCAD simulations

- $\rightarrow$  studies ongoing

- Goal: homogeneous electrical field distribution

#### **Implementation and Verification**

- One optimized geometry chosen for all matrices

- In first columns of matrix A different pixel geometries will be implemented to allow studies and verification

9

#### **Pixel Cell - Amplifier**

#### **Properties**

- Amplifier in pixel

- Every pixel maskable

#### **CMOS** Amplifier

- Implemented in ATLASPix 3

- Uses vdda = 1,8 V

no additional voltage needed

- Matrix C

#### **PMOS Amplifier**

- Implemented in MuPix 8

- Vssa needed = 0,9 V

- Used successfully in many chips

- Matrix A and B

#### **Signal Transmission**

#### Source follower

Implemented in MuPix 8 matrix A

#### **Current driver**

- Implemented in MuPix 8 matrices B and C

- Small design modifications needed

# High R UNIVERSITÄT SIT 1386 Karlsruher Institut für Technologie

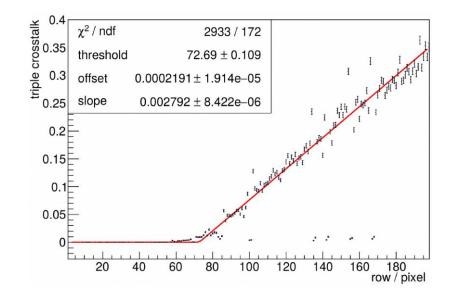

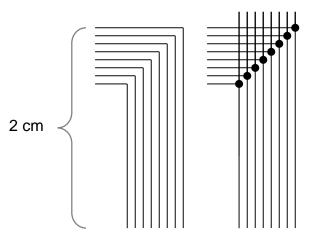

#### Routing

- For routing in total 3 metal layers

- Routing scheme similar to ATLASPix 3

- same line length

- all lines with same shape

- requires more time for routing

- suppression of row-dependent change of pulse shape

- more homogeneous time resolution

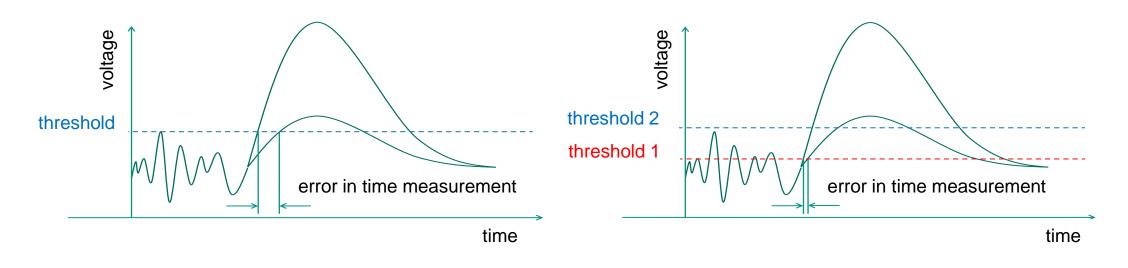

### **Readout Cell**

#### **2** Threshold Method

- 2 Comparators per pixel like MuPix 8

- 3 bits per readout cell for threshold tuning

- Lower threshold voltage provides timestamp with less timewalk

- Higher threshold confirms signal

#### Data Rate

- 11 bits for timestamps

1 bit more then MuPix 8

- 5 bits for TOT one bit less then MuPix 8

- $\rightarrow$  same data format like MuPix 8

- sampling frequency 250 MHz

#### **Chip Readout and Pads**

#### Readout

- 3 LVDS links (one for every matrix)

- 1 LVDS link with multiplexed signals

- Max. LVDS data rate 1.6 Gbit/s

#### Monitor internal signals

- Temperature

- Amplifier output

- Hitbus

- Bandgap voltage

- Power regulated voltages

#### Pads

Minimized number of inputs and outputs to run the chip

Highℝ

- All pads at the bottom

- Enough space for test to monitor internal signals

- Suitable for TAB-bonding

UNIVERSITÄT HEIDELBERG ZUKUNFT

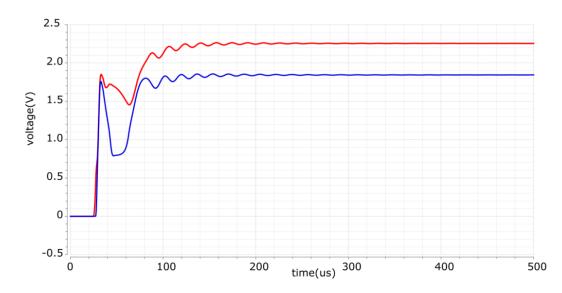

#### **Power Regulator**

#### **Properties**

- In Mu3e: one supply voltage: 2.0 2.2 V

- Generates stable 1.8 V and 0.9 V

- Controlled by slow control

- Power separated:

- Analogue and digital part separated

- Capacitively coupled

- Allow different voltage levels for optional serial powering with different schemes

#### HighR High R Hig

#### Status

- Power regulator designed for ATLASPix and MuPix

- Actual design submitted with ATLASPix 3

Simulation of 4 chips with power regulator connected in parallel

#### Summary

- Full size

- Suitable for module building

- A lot of features in one chip old ones, improved ones, new ones

- Different options in one chip including the final MuPix design

- Last prototype

- Final chip based on MuPix 10

Photo of the existing mockup

# BACKUP

# Important features from other chips for MuPix 10

- 2 threshold mode MuPix 8

- 3 submatrices MuPix 8

- Pixels with PMOS amplifier MuPix 8

- Slow control MuPix 9

- Analog and digital power supply separated and capacitive coupled MuPix 9

- Power Regulator MuPix 9 and ATLASPix 3

- Pixels with CMOS amplifier ATLASPix 3

## **Power Regulator**

- Only one supply voltage: 2.0 2.2 V

- Similar Power Regulator developed and implanted on ATLASPix 3, submitted in March

- Based on the results of the measurements of this power regulator the circuit will be optimised for MuPix 10

- Power Regulators controlled by slow control

- Power Regulators can be bypassed

- Power Up Reset with max 1 ms length

- chip in standby

- chip can be configured  $\rightarrow$  slow control is the only powered part

- power regulators disabled

- single chips tests without cooling possible

- Analogue and digital part separated regarding to power and capacitively coupled

$\rightarrow$  allow different voltage levels for optional serial powering with different schemes  $\rightarrow$  implemented in MuPix 9  $\checkmark$