JGU JOHANNES GUTENBERG UNIVERSITÄT MAINZ Firmware and Synchronisation of the First Layer in the Mu3e DAQ System Martin Müller, DPG Spring Meeting 2021

| 1.~~ | Intro | oduction | DAQ System | FE Board | Synchronization | Outlook |

|------|-------|----------|------------|----------|-----------------|---------|

| 3D   | Mu3e  |          |            |          |                 |         |

| es   |       |          |            |          |                 |         |

|      |       |          |            |          |                 |         |

## Mu3e

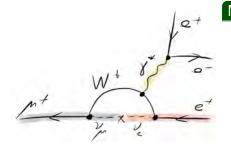

- search for the lepton flavour violating decay  $\mu^+ \to e^+ e^- e^+$

- predicted branching ratio of 10<sup>-54</sup> (not observable)

- observation of  $\mu^+ \rightarrow e^+ e^- e^+$ would be a clear sign for new Physics

| 1.~~ | Introduction         | DAQ System | FE Board | Synchronization | Outlook |

|------|----------------------|------------|----------|-----------------|---------|

| 3D   | Introduction         |            |          |                 |         |

| C    | Background processes |            |          |                 |         |

Background processes:

$$\bullet \mu^+ \to \mathrm{e}^+ \nu_\mathrm{e} \overline{\nu}_\mu \mathrm{e}^+ \mathrm{e}^-$$

combinatorial

For signal events:  $\sum ec{p} = 0, \ \sum E = m_\mu, \ \Delta t = 0$ , same vertex

Low electron momenta  $\rightarrow$  multiple scattering  $\rightarrow$  material budget

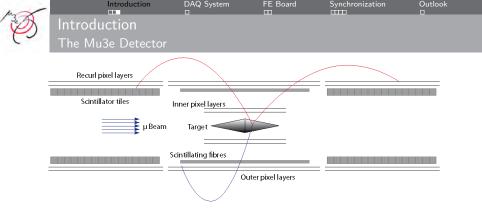

- 4 layers of pixel sensors ( $\sigma t = 10 \text{ ns}$ )

- scintillating fibres ( $\sigma t =$ 500 ps) & tiles ( $\sigma t =$ 70 ps) to increase timing precision

- $\blacksquare \rightarrow$  need time synchronization (clock and reset) to this precision

- expected data rate of up to 80 GBit/s

| 1.~~ | Introduction | DAQ System | FE Board | Synchronization | Outlook<br>□ |  |

|------|--------------|------------|----------|-----------------|--------------|--|

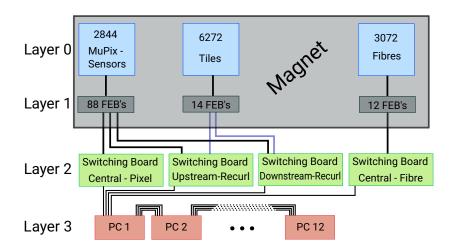

| B    | DAQ System   |            |          |                 |              |  |

| (5   | Overview     |            |          |                 |              |  |

| 1.~~ |         | Introduction | DAQ System | FE Board | Synchronization | Outlook |

|------|---------|--------------|------------|----------|-----------------|---------|

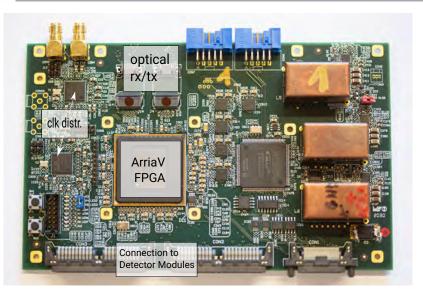

| 3D   | FE Boa  | rd           |            |          |                 |         |

| (5   | FE Boar | d            |            |          |                 |         |

| 1.~~ | Introduction     | DAQ System | FE Board | Synchronization | Outlook<br>□ |  |

|------|------------------|------------|----------|-----------------|--------------|--|

| 30   | FE Board         |            |          |                 |              |  |

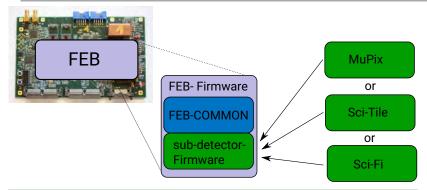

| ()   | Firmware concept |            |          |                 |              |  |

## $\mathsf{Common} \leftrightarrow \mathsf{sub-detector} \mathsf{Interface}$

- Detector data

- access to slowcontrol system

- run state signals

- confirmation of run state changes

| 1.~~ | Introduction    | DAQ System | FE Board | Synchronization | Outlook<br>□ |

|------|-----------------|------------|----------|-----------------|--------------|

| 3-D  | Synchronization |            |          |                 |              |

| 63   | Reset idea      |            |          |                 |              |

|      |                 |            |          |                 |              |

- I run starts need to happen in the same clock cycle for all components in the detector

- 2  $\rightarrow$  time window of 1 global clock cycle (125 MHz) where the reset has to arrive

- $\mathbf{3}$   $\rightarrow$  re-synchronise reset to global clock at detector-asic level

- 4 ightarrow reset with precision of clock distribution

## $\rightarrow$ Additional optical Reset line.

| 1.~~ | Introduction        | DAQ System | FE Board | Synchronization | Outlook |

|------|---------------------|------------|----------|-----------------|---------|

| 30   | Synchronization     |            |          |                 |         |

| 65   | Clock and Reset Box |            |          |                 |         |

Martin Müller

| 1.~~ | Introduction       | DAQ System | FE Board | Synchronization | Outlook<br>□ |

|------|--------------------|------------|----------|-----------------|--------------|

| 32   | Synchronization    |            |          |                 |              |

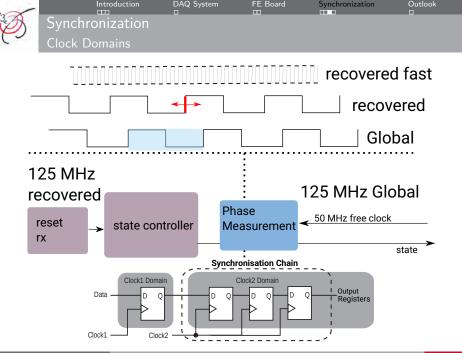

| C    | Phase measurements |            |          |                 |              |

|      |                    |            |          |                 |              |

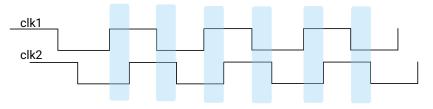

- using independent, free running clock with frequency f

- measurement time T

- count clk1 != clk2 events on rising edge of independent clock

- $\rightarrow$  phase difference =  $\frac{counts}{T \cdot f} \cdot \pi$

We can use this measurement to check if the reset is synchronized even without physical access to the board

- system was operated for the first time with all sub-detectors at DESY last Year.

- Preparation for the first test run with a pixel vertex detector and timing detectors inside the Mu3e Magnet at PSI is ongoing