## Department of Physics and Astronomy University of Heidelberg

Master thesis

in Physics

submitted by

Lennart Huth

born in Buchen

2014

# Development of a Tracking Telescope for Low Momentum Particles and High Rates consisting of HV-MAPS

This Master thesis has been carried out by Lennart Huth at the

Physikalisches Institut under the supervision of Herrn Prof. Dr. André Schöning

## Development of a Tracking Telescope for Low Momentum Particles and High Rates consisting of High-Voltage Monolithic Active Pixel Sensors

Physics beyond the Standard Model (SM) of particle physics motivates the search for the charged lepton flavor violating decay  $\mu^+ \to e^+e^-e^+$  by the Mu3e experiment. This decay is suppressed with a branching ratio below  $10^{-54}$  within the SM. Detecting this decay would be a clear sign for new physics beyond the SM. Reaching the aimed sensitivity of better than one in  $10^{16}~\mu^+-$  decays in a reasonable time requires excellent momentum and vertex resolution for background suppression at high decay rates  $\mathcal{O}(10^9\mu/\text{s})$ . The maximum energy of 53 MeV of the decay particles results in a multiple scattering limited vertex and momentum resolution requiring a detector with little material. These requirements will be fulfilled by a pixel detector consisting of 50  $\mu$ m thin High-Voltage Monolithic Active Pixel Sensors (HV-MAPS) with a time resolution of better than 20 ns.

A low momentum particle tracking telescope was developed to test the detector components and the data acquisition (DAQ) to perform a first integration test of the Mu3e detector and to use it at the Paul-Scherrer-Institue (PSI). The development of the mechanics and DAQ and the results of two testbeam campaigns is presented: It is shown that the readout concept of the telescope is working and that the sensors can be synchronized. It also can handle high particle rates  $\mathcal{O}(600~\text{kHz})$ . The mechanical alignment can be carried out with a high precision  $\mathcal{O}(100~\mu\text{m})$ . Furthermore it is shown that the particle track reconstruction works for 5 GeV electrons with thick sensors of 2 % of radiation length. All measurements are supported by additional simulations.

## Entwicklung eines Strahlteleskops für niederenergetische Teilchen und hohe Raten basierend auf hochspannungsbetriebenen monolithischen aktiven Pixelsensoren

Physik jenseits des Standardmodells (SM) der Teilchenphysik motiviert die Suche nach dem geladenen Lepton-Zahl verletzenden Zerfall  $\mu^+ \to e^+e^-e^+$  durch das Mu3e Experiment. Dieser ist im SM mit einem Verzweigungsverhältnis von weniger als  $10^{-54}$  unterdrückt und dessen Beobachtung wäre daher ein klares Zeichen für neue Physik. Um die angestrebte Sensitivität von weniger als einem in  $10^{16}~\mu^+$  – Zerfällen in einer angemessenen Zeit zu erreichen, wird eine hohe Zerfallsrate von  $\mathcal{O}(10^9\mu/\mathrm{s})$  sowie exzellente Vertex-, Impuls- und Zeitauflösung zur Untergrundunterdrückung benötigt. Durch die geringe maximale Energie von 53 MeV der Zerfallsteilchen ist die Energie- und Impulsauflösung von Vielfachstreeung dominiert. Dies erfordert einen dünnen Detektor.

Um diese Anforderungen zu erfüllen, wird der Pixeldetektor von Mu3e aus dünnen, bei Hochspannung betriebenen monolithischen aktiven Pixelsensoren (HV-MAPS) gebaut, die am Physikalischen Institut der Universität Heidelberg charaktersiert werden.

Um die Detektorkomponenten und die Datennahme des Mu3e-Detektors zu testen, sowie einen ersten Integrationstest durchzuführen und es am PSI einzusetzen, wurde ein Strahlteleskop aus HV-MAPS realisiert. Die mechanische Konstruktion, das Datennahmesystem und die Analyseprogramme werden vorgestellt. Außerdem wird der Einsatz bei zwei Strahlzeiten und deren Ergebnisse erläutert. Es wird gezeigt, dass es möglich ist ein synchronisiertes Teleskop aus HV-MAPS zu betreiben, welches hohe Teilchenraten  $\mathcal{O}(600\text{kHz})$  verarbeiten kann. Außerdem ist es möglich das System mechanisch mit einer Präzision von  $\mathcal{O}(100~\mu\text{m})$  auszurichten. Des weiteren wird gezeigt, dass die Spurrekonstruktion trotz der noch ungedünnten Sensoren, d.h. mit 2 ‰ Strahlungslänge, gute Resultate für Elektronen mit einem Impuls von 5 GeV liefert. Die Ergebnisse der Strahlzeiten lasssen sich anhand von Simulationen verifizieren.

## **Contents**

| Co | nten                     | ts                                                                                                                                                                                                                                                         | 6                                                        |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Ι  | Intr                     | roduction                                                                                                                                                                                                                                                  | 11                                                       |

| 1  | <b>The</b> 1.1           | Standard Model of Particle Physics Muon Decays                                                                                                                                                                                                             | <b>1</b> 5                                               |

| 2  | Mu3 2.1 2.2              | Be - Search for New Physics at the High Rate Frontier  Experimental Situation The Mu3e Experiment  2.2.1 Signal Decay  2.2.2 Backgrounds  2.2.3 Requirements  2.2.4 Experimental Concept  2.2.5 Sub Detectors  2.2.6 Readout Concept  2.2.7 Muon Beam      | 19<br>19<br>20<br>21<br>21<br>22<br>23<br>23<br>25<br>26 |

| 3  | Part                     | icle Interaction and Detection                                                                                                                                                                                                                             | 29                                                       |

|    | 3.1<br>3.2<br>3.3<br>3.4 | Particle Interactions with Matter  Multiple Coulomb Scattering  Particle Tracking Detectors  3.3.1 Silicon Pixel Detectors  3.3.1.1 MAPS  3.3.2 HV-MAPS  Data Transfer and Readout  3.4.1 Field Programmable Gate Arrays (FPGA)  3.4.2 Signal Transmission | 29<br>30<br>31<br>32<br>33<br>33<br>34<br>34<br>35       |

| 4  | Part 4.1 4.2 4.3 4.4     | icle Track Reconstruction  Coordinate System                                                                                                                                                                                                               | 37<br>37<br>37<br>38<br>40                               |

8 Contents

| II | Set  | tup & Measurements                                 | 41  |

|----|------|----------------------------------------------------|-----|

| 5  | The  | MuPix Telescope                                    | 43  |

|    | 5.1  | Motivation                                         | 43  |

|    | 5.2  | Telescope Concept                                  | 44  |

|    | 5.3  | Mechanics                                          | 46  |

|    |      | 5.3.1 PCB Holders                                  | 47  |

|    | 5.4  | MuPix Prototypes                                   | 49  |

|    |      | 5.4.1 Sensor Electronics                           | 49  |

|    |      | 5.4.2 Hit Storage                                  | 51  |

|    |      | 5.4.3 MuPix Readout                                | 51  |

|    |      | 5.4.4 Special Characteristics of the Prototypes    | 53  |

|    | 5.5  | Electronics and Cabling                            | 53  |

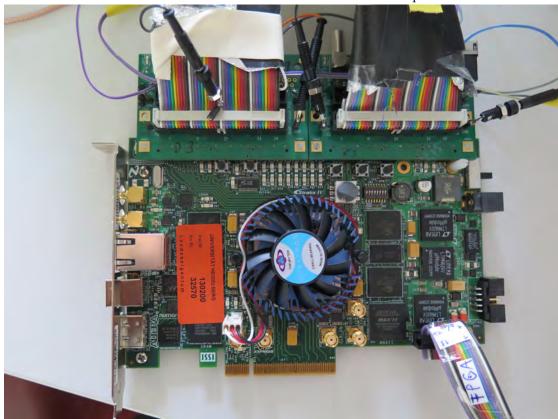

|    | 5.5  | 5.5.1 Stratix IV Development Board                 | 54  |

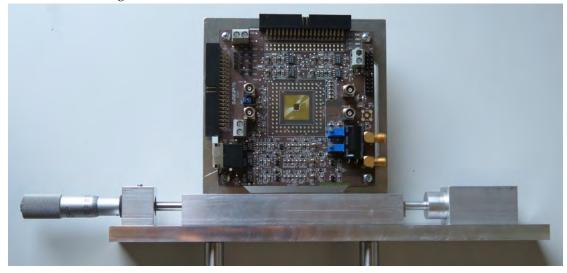

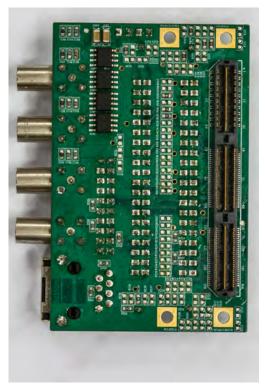

|    |      | 5.5.2 The MuPix Test Board                         | 54  |

|    |      |                                                    |     |

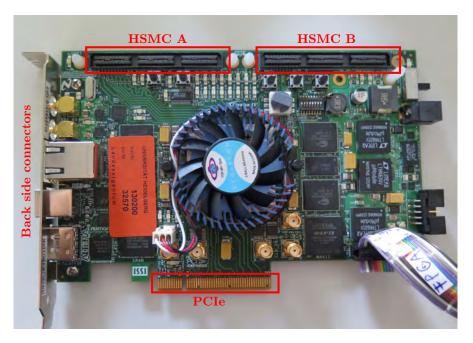

|    |      | 5.5.3 HSMC Adapter Cards                           | 55  |

|    |      | 5.5.4 LVDS Cards                                   | 56  |

| 6  | Data | a Acquisition                                      | 59  |

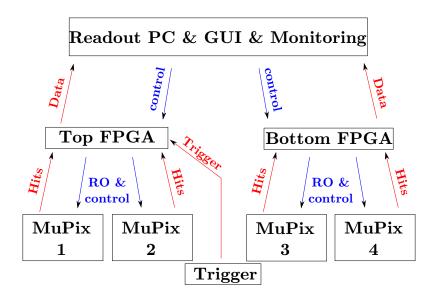

|    | 6.1  | DAQ-Concept                                        | 59  |

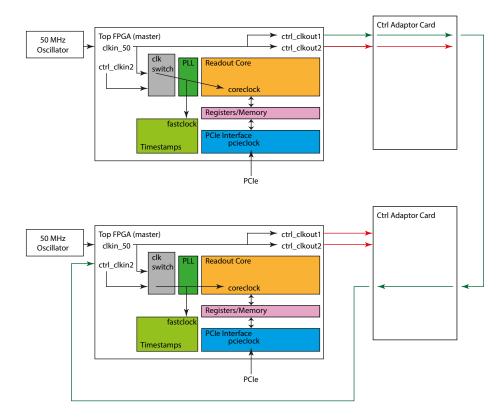

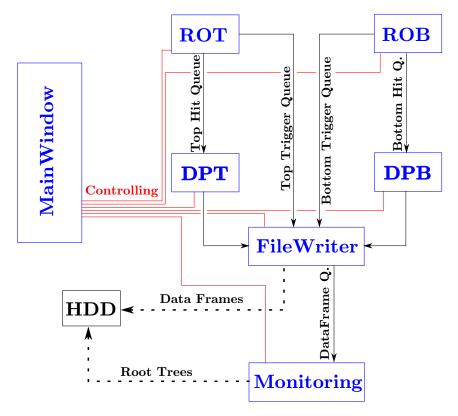

|    | 6.2  | Telescope Readout Firmware                         | 60  |

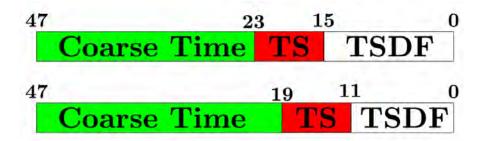

|    | 6.3  | FPGA Time Information and Synchronization          | 61  |

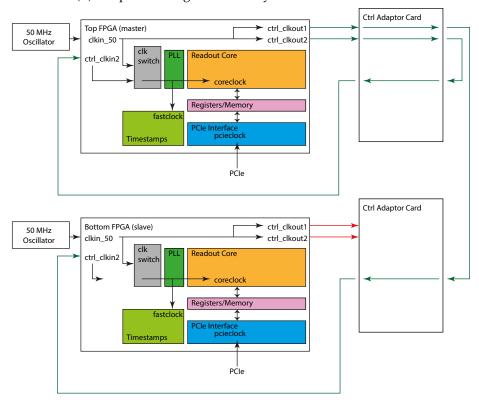

|    | 6.4  | Readout Software                                   | 65  |

|    |      | 6.4.1 Threads:                                     | 67  |

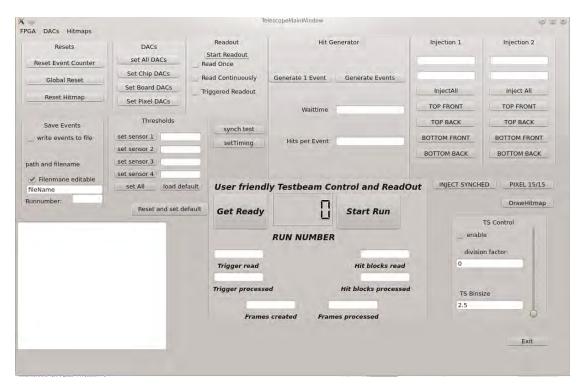

|    | 6.5  | The MainWindow                                     | 68  |

|    | 6.6  | Online Monitoring                                  | 72  |

| _  |      |                                                    |     |

| 7  |      | ulations                                           | 73  |

|    | 7.1  | Event Generation                                   | 73  |

|    | 7.2  | Track Reconstruction Algorithm Structure           | 76  |

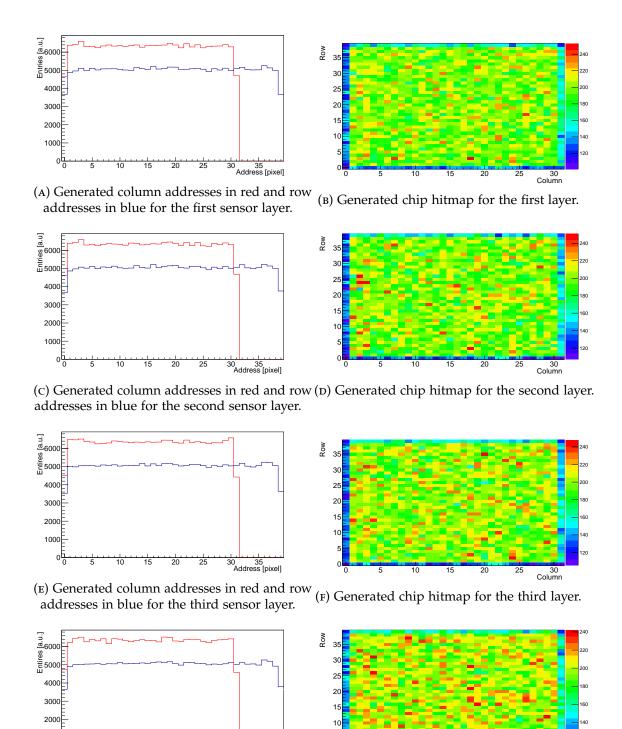

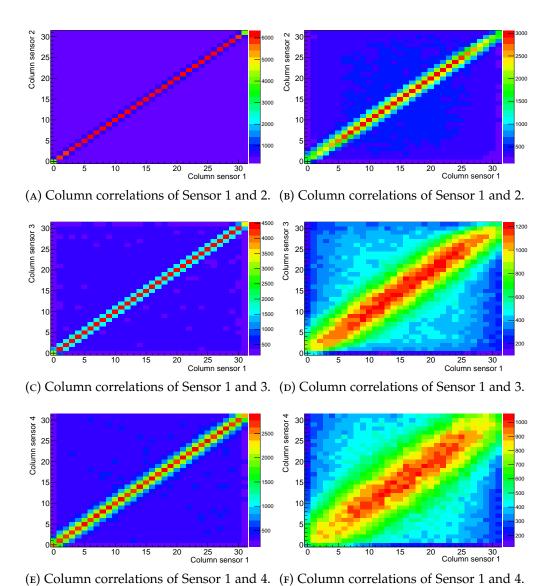

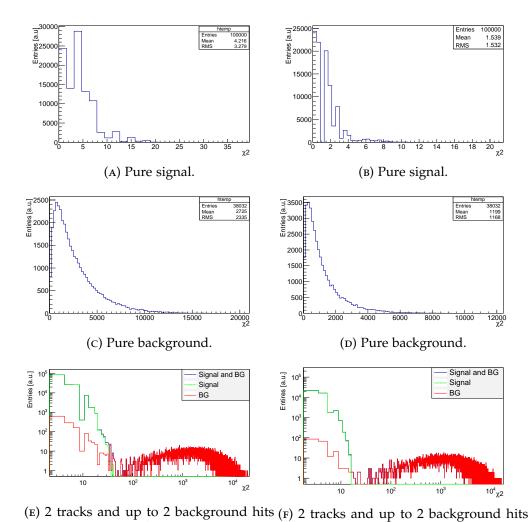

|    | 7.3  | Validation of Event Generation                     | 77  |

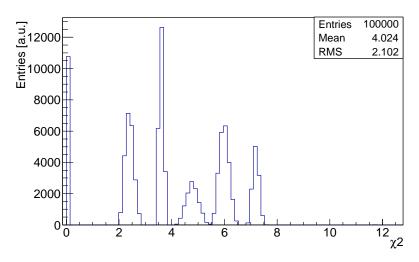

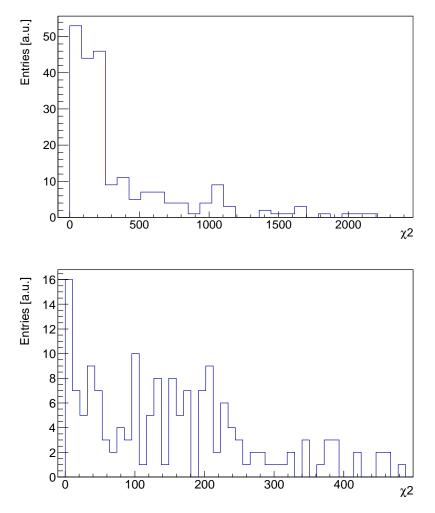

|    | 7.4  | Validation of the Track Reconstruction             | 80  |

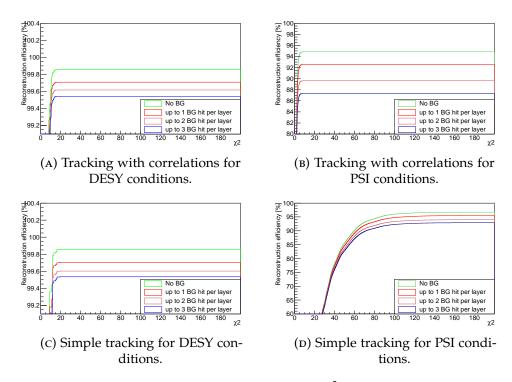

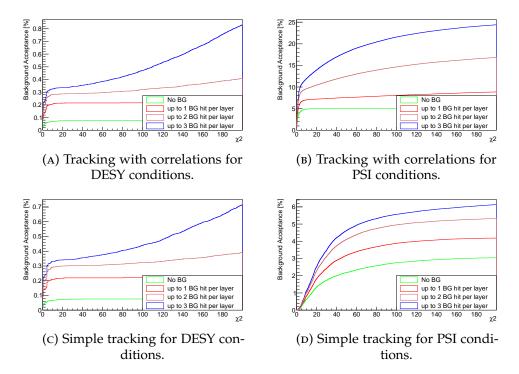

|    | 7.5  | Comparison of the Track Reconstruction Methods     | 81  |

|    | 7.6  | Reconstruction Efficiency and Background Rejection | 82  |

| 8  | DES  | SY T22 Testbeam                                    | 87  |

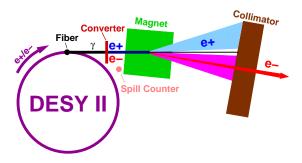

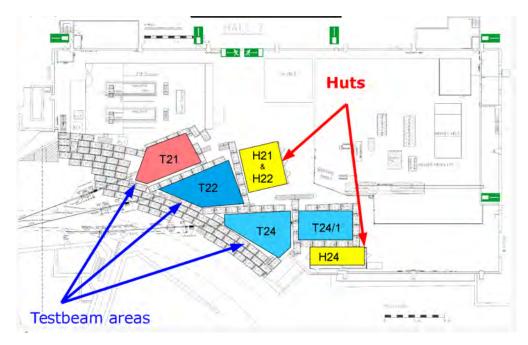

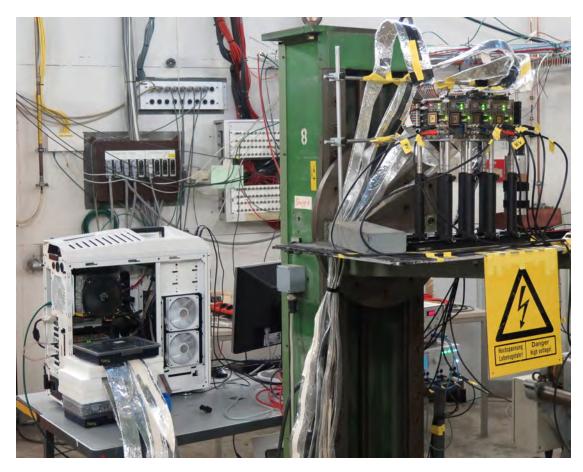

| Ü  | 8.1  | Setup                                              | 88  |

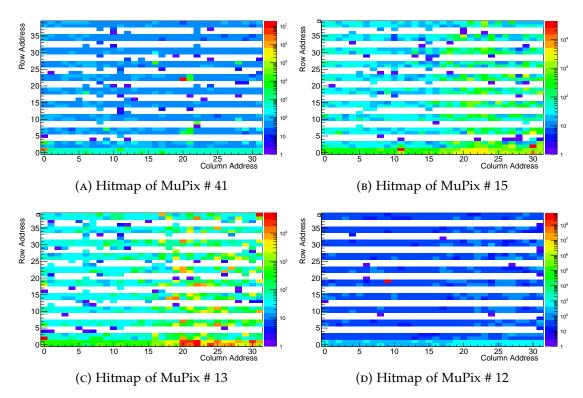

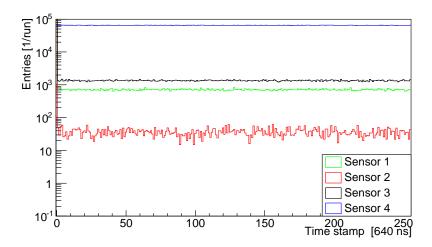

|    | 8.2  | Data Taking & Performance                          | 90  |

|    | 8.3  | Analysis                                           | 95  |

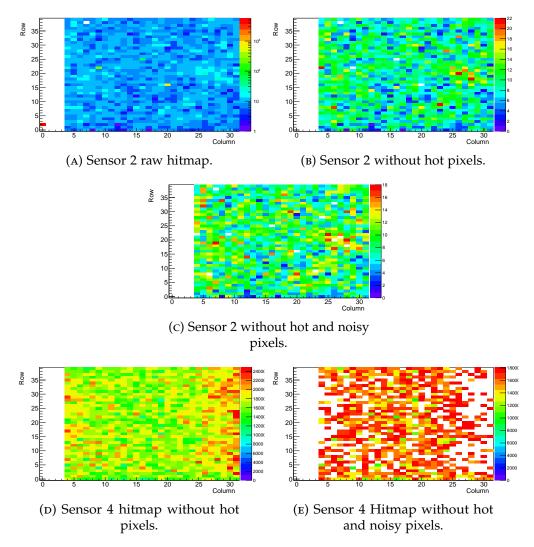

|    | 8.4  | Hot Pixel Removal                                  | 95  |

|    |      |                                                    |     |

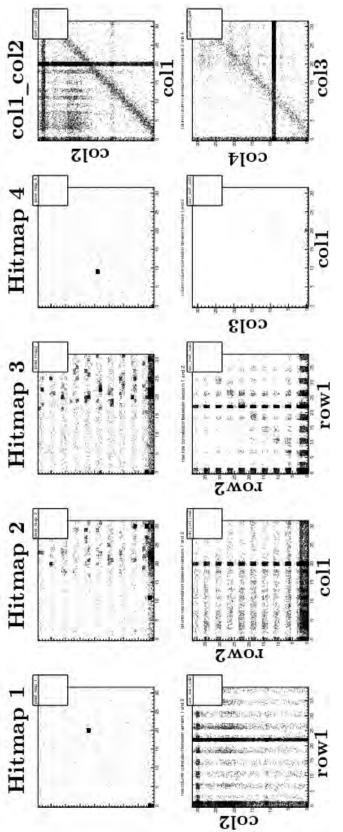

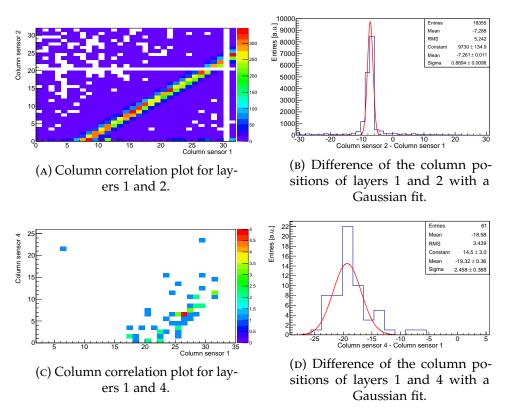

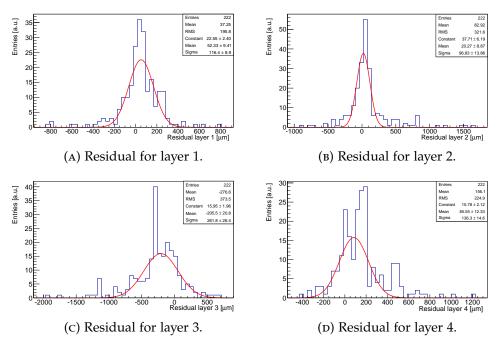

|    | 8.5  | Telescope Alignment                                | 96  |

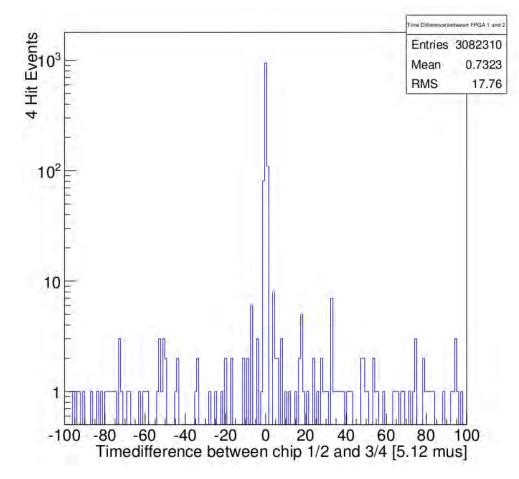

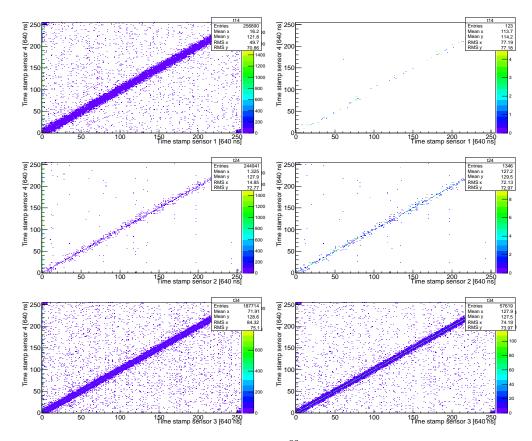

|    |      | 8.5.1 Timing and Synchronization                   | 97  |

|    | 0 -  | 8.5.2 Track Reconstruction                         | 98  |

|    | 8.6  | Summary                                            | 101 |

| 9  | PSI  | $\pi$ M1 Testbeam                                  | 103 |

|    | 9.1  | Setup                                              | 103 |

|    | 9.2  | Performance                                        | 105 |

|     | 9.3              | 9.3.1         | Tsis                        | <br> | 107               |

|-----|------------------|---------------|-----------------------------|------|-------------------|

| III | Co               | onclus        | ions                        |      | 113               |

| 10  | 10.1             | Summ          | & Outlook  nary             |      | 115<br>115<br>116 |

| IV  | ' A <sub>I</sub> | ppendi        | ix                          |      | 119               |

| A   | Trac             | k Fittin      | ng                          |      | 121               |

| В   | Gray             | Code          | Converter                   |      | 123               |

| C   | Digi             | tal to F      | Physical Address Conversion |      | 125               |

| D   | FPG              | A Com         | nmunication                 |      | 127               |

| E   | DAC              | C Settir      | ngs                         |      | 131               |

| Lis | st of I          | Figures       | 3                           |      | 132               |

| Lis | st of T          | <b>Fables</b> |                             |      | 135               |

## Part I

## Introduction

### Introduction

One challenge in modern physics is the search for new physics beyond the Standard Model (SM) of particle physics. This search can be done in different ways. On the one hand, one can increase particle energies and try to directly produce new heavy particles. This idea is followed by experiments at large accelerators like the Large Hadron Collider (LHC) or the planned International Linear Collider (ILC). On the other hand, one can go to high particle rates to find very rare decays, which are forbidden or suppressed down to an unobservable level in the SM. This research can be done with relatively small accelerators, which deliver a high number of low momentum particles, like the High Intensity Proton Accelerator (HIPA) at the Paul-Scherrer-Institute (PSI) in Switzerland. Both research fields require new detector concepts. For completeness, it should be also mentioned that the search for new physics can also be done by searching for dark matter.

The Mu3e experiment aims to find the decay of a muon into three electrons, which is strongly suppressed in the SM or to give an upper limit on the branching ratio of this decay in the order of  $10^{-16}$ . Therefore, an intense muon beam of  $2 \cdot 10^9$  muons per second is needed to perform the experiment on an appropriate timescale. The currently existing beamline at PSI provides up to  $10^8$  muons per second. A new High intensity Muon Beamline (HiMB) could provide the required rate of  $2 \cdot 10^9$  muons per second. In order to be sensitive to such a rare decay, one has to build a detector with very high momentum resolution, excellent vertex reconstruction and low noise to suppress background below the aimed sensitivity level. The material budget in the active region has to be minimized to reduce multiple Coulomb scattering, which limits the vertex and momentum resolution at low particle momenta. The last important issue is to have an excellent timing to reduce combinatorics.

This can be achieved by the use of a novel silicon pixel design, the so called High Voltage Monolithic Active Pixel Sensor (HV-MAPS). The main advantages of this technology are the fast pixel readout, which reduces the dead time of the detector, and the fact that the electronics of the chip is directly implemented in the active area. Therefore no additional separate electronic layer is required, which would introduce additional material. Due to the thin active area the chip can be thinned down to less than 50  $\mu$ m. The high event multiplicity additionally requires very precise timing in the order of 100 ps. This requirement can be met by scintillating fibers and tiles, which are also

included in the detector design.

All new devices have to be tested, characterized and specified for the usability in the Mu3e experiment. Therefore, the MuPix HV-MAPS prototypes are characterized in the lab at the Physikalisches Institut (PI) in Heidelberg and in test beams at DESY in Hamburg, at CERN and at PSI in Villigen. At DESY, the spatial resolution of prototypes can be determined with the EUDET-telescope installed in test beam area T22. At PSI such a beam telescope is not available.

These particle tracking telescopes are an important tool to characterize new devices. The MuPix sensor is a perfect candidate to build such a telescope due to its properties. In addition, the HV-MAPS technology can handle high particle rates and allows for thin sensors suitable for low momentum particle tracking. The MuPix sensor characterization at PI provides all the needed electronics and support structure to build a telescope. Due to these advantages and as an integration test, it was decided to build a standalone, flexible and compact low momentum particle tracking telescope from the MuPix prototypes at the PI in Heidelberg.

The goal of this thesis is to develop such a telescope. Therefore a new mechanical structure is designed and relaized, which is used to mount the telescope planes. The electronics of four single sensors have to be connected to a common readout computer and synchronized. Also a DAQ software has to be developed, based on the DAQ software for the single MuPix test setup.

At the beginning, the SM and Lepton flavor violating decays are explained, which motivate the MU3e experiment that is discussed afterwards. In the third chapter, the interaction of particles with matter and their detection is discussed in more detail, followed by a introduction in particle track reconstruction, focusing on straight tracks. The fifth chapter introduces the MuPix telescope and discusses the used components adapted from the Mu3e experiment in detail. The following chapter examines the data acquisition system and explains the graphical user interface. The simulations of the telescope are addressed in the seventh chapter. Chapter eight and nine discuss the two testbeam campaigns carried out and their results. At the end, the work is summarized and an outlook is given.

## Chapter 1

## The Standard Model of Particle Physics

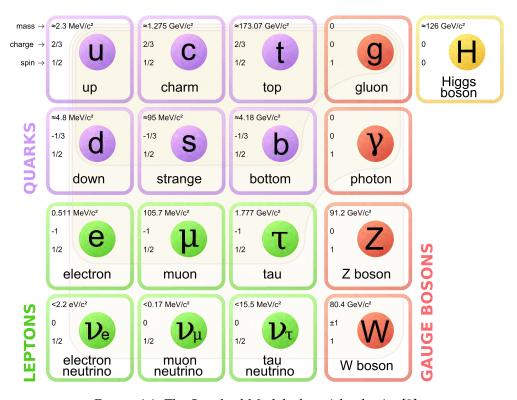

The Standard Model (SM) of particle physics [1] is a quantum field theory describing the smallest constituents of matter, the elementary particles, and their interactions. Figure 1.1 shows a schematic view of the particle content of the SM, consisting of six quarks (and anti quarks), six leptons (and anti leptons), four gauge bosons and the Higgs boson.

FIGURE 1.1: The Standard Model of particle physics [2].

The quarks and leptons are arranged in three generations and the interactions between them are mediated by the gauge bosons. The first generation consists of the two lightest quarks up (u) and down (d) with a charge of +2/3 and -1/3, respectively, the electron (e<sup>-</sup>) with an electric charge of -1 and the neutral electron neutrino ( $\nu_{e^-}$ ). The second and third families look similar: Two quarks, one charged lepton and one neutrino with the same quantum numbers, but with different masses. The second family consists of the charm (c) and the strange (s) quark, the muon ( $\mu^-$ ) and the muon neutrino ( $\nu_{\mu}$ ), while the third family contains the top (t) and bottom (b) quarks, the tau ( $\tau^-$ ) and the tau neutrino ( $\nu_{\tau}$ ). The neutrinos are assumed to be massless in the SM, while the lepton flavour number (the number of leptons minus anti leptons from the same family) is conserved in every decay.

All particles from the three families are spin 1/2 particles, the so called fermions interact via the exchange of gauge bosons which are spin 1 particles. The interactions between the particles are classified in three groups: The electromagnetic interaction is mediated by the photon ( $\gamma$ ), the eight gluons are responsible for the strong interaction and the Z, W<sup>+</sup> and W<sup>-</sup> mediate the weak interaction.

The SM is one of the most successful theories in modern physics and is confirmed by numerous experiments. Especially the discovery of the long ago predicted Higgs boson at the LHC [3, 4] has shown, that the SM is consistent: The Higgs boson is a manifestation of the Higgs field responsible for the symmetry breaking between the electromagnetic and weak interactions (i.e. the larger masses of the W and Z bosons).

Nevertheless there are many effects, that can not be explained by the SM, like neutrinos oscillating between different flavour eigenstates, which is observed in many experiments like SNO [5], Daya-Bay [6], Super-Kamiokande [7]. This is only possible by introducing mass differences between the neutrino mass eigenstates. One way is expanding the SM by introducing a heavy right-handed neutrino, which gives a small mass to the left-handed ones (the so called seesaw mechanism [8]). Even if neutrino oscillations can be explained with an extended SM, there are still many open questions: Why do we only have 3 families? How can gravity be explained? Why do we have a matter - antimatter asymmetry in the universe? What is the origin of dark matter? What happens at higher energies? Is the charged lepton flavor conserved in all decays?

Those questions are linked to many new theories (beyond the SM) which try to explain those effects and predict new particles. Those theories have to be verified by new experiments, reaching higher energies and/or higher rates.

#### 1.1 Muon Decays

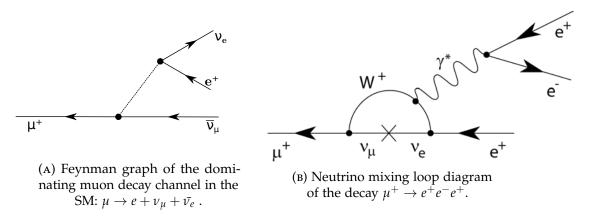

Many models for physics beyond the standard model predict measurable amounts of charged lepton flavour violation (cLFV) processes. cLFV could be observed in the decays of leptons, such as muon decays. The dominating muon decay into two neutrinos and an electron is shown in Figure 1.2a.

One possible LFV muon decay is the decay  $\mu^+ \to e^+e^-e^+$ , which is forbidden on

FIGURE 1.2: Feynman graphs of possible SM muon decays.

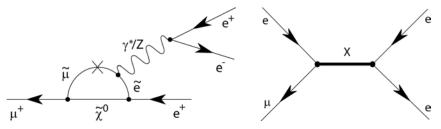

tree level in the SM and can therefore only happen via higher order loop corrections with neutrino oscillation (compare Figure 1.2b). This decay is strongly suppressed in the SM with a branching ratio (BR) of below  $10^{-54}$ . Therefore it is not observable and any observation would be a very clear hint for new physics beyond the SM. There are several theories predicting an increased BR for this decay, like  $\gamma/Z$  penguin diagrams with a loop of supersymmetric (SUSY) particles or tree diagrams with new particles like heavy vector bosons, doubly charged Higgs or scalar neutrinos. Two possible diagrams are shown in Figure 1.3.

- (A) Penguin diagram with a SUSY loop.

- (B) Tree diagram with new particles.

Figure 1.3: Feynman diagrams for  $\mu^+ \to e^+e^-e^+$  assuming beyond SM physics.

## Chapter 2

## Mu3e - Search for New Physics at the High Rate Frontier

As mentioned in the introduction, the search for new physics is a central and challenging part of modern particle physics. In the following the research in the context of high rate experiments in the muon sector is addressed. At the beginning a rough overview over the current experimental situation is given. The second section discusses the Mu3e experiment in detail, beginning with the signal decay followed by the main backgrounds and the resulting requirements. Subsequently the experimental concept and the used detectors are introduced. At the end, the muon beam available at PSI is discussed.

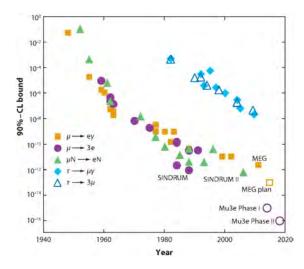

#### 2.1 Experimental Situation

In the year of 1953, the first experiment searching for charged lepton flavor violation in muon decays started data taking. Up to now no signal was found, only upper limits on branching ratios were achieved. The best limit on the  $\mu^+ \to e^+e^-e^+$  branching ratio is set by SINDRUM [9], while MEG [10] is leading in the  $\mu \to e \gamma$  search.

#### **SINDRUM**

The SINDRUM [9] experiment searched from 1983 to 1986 for the process  $\mu^+ \to e^+e^-e^+$  and did not detect any signal. They set a limit on the branching ratio of BR( $\mu^+ \to e^+e^-e^+$ ) < 10<sup>-12</sup> at 90% confidence level (C.L.). The SINDRUM detector was placed at PSI and consisted of a hollow double cone target to stop 28 MeV/c surface muons in a solenoid magnetic field of 033 T. The target was surrounded by five tracking layers of multiwire proportional chambers and a trigger hodoscope. The main background

FIGURE 2.1: The history of LFV muon decay research, adapted from [11].

was given by the decay  $\mu^+ \to e^+ e^+ e^- \overline{\nu_{\mu}} \nu_e$  which was estimated to be  $5 \cdot 10^{-14}$ . So the published SINDRUM result was only limited by the number of stopped muons.

#### **MEG**

The MEG experiment [10] searches for the LFV decay  $\mu^+ \to e^+ \gamma$  and is in operation since 2008. The main detection concept is to detect the positron in a drift chamber and the photon in a liquid Xenon calorimeter. The MEG-system was updated after the run time in 2008 and the data analysis yielded to an upper limit of BR( $\mu^+ \to e^+ \gamma$ ) < 5.7 · 10<sup>-13</sup> [12]. The MEG detector will be upgraded [13] and is supposed to continue searching for  $\mu \to e \gamma$ .

#### 2.2 The Mu3e Experiment

Mu3e [14] is an experiment, which searches for the lepton flavor violating decay of a positive muon into two positrons and one electron and aims for a high sensitivity, requiring  $2 \cdot 10^9$  muons per second. Such an intense beam does not exist at the moment, but could be realized at PSI after 2019 [15]. To handle the large amount of data, a non triggered readout with fast online track reconstruction is proposed. To suppress background, excellent timing with a time resolution of  $\mathcal{O}$  (100 ps) as well as fast and good vertex reconstruction with a spatial resolution  $\mathcal{O}$  (100 µm) is required for the online event filter.

#### 2.2.1 Signal Decay

The  $\mu^+ \rightarrow e^+e^-e^+$  decay signal has a vanishing total momentum

$$\vec{p}_{tot} = \sum_{i=0}^{2} p_i = 0 \tag{2.1}$$

because the muons decay at rest. The total energy has to be equal to the muons rest mass of  $105.659 \text{ MeV/}c^2$  [1]:

$$E_{tot} = \sum_{i=0}^{2} E_i = m_{\mu} \cdot c^2. \tag{2.2}$$

Equation 2.1 restricts the electrons energy between  $m_e c^2$  and 1/2  $m_{\mu} \approx 53$  MeV.

#### 2.2.2 Backgrounds

The detection of a very rare decay requires a good understanding of backgrounds and the possibility to suppress them down to a level below the desired sensitivity. The two critical backgrounds are random combinations and internal conversion.

#### Random Combination Background

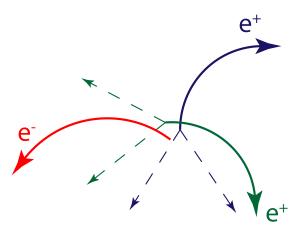

The high rate operation of Mu3e leads to many decays. The probability to find a configuration similar to the  $\mu^+ \to e^+e^-e^+$  signal by random combinations is quite high: Two positrons from Michel decays (the dominant muon decay, shown in Figure 1.2a) can combine with an electron from a photon conversion process or mis-reconstruction (see Figure 2.2). Since the particles originate from different decays, they do not share a common vertex and most likely the sum of their momenta and energy does not vanish. In addition, the decays do likely not happen exactly at the same time. This background can be efficiently suppressed by excellent time, momentum and spatial resolution.

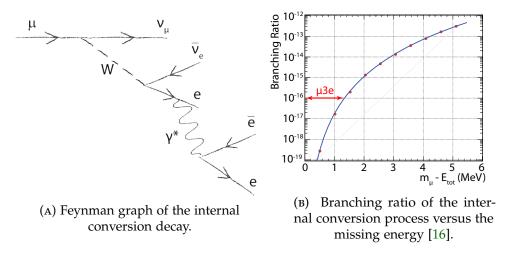

#### **Internal Conversion**

The second and most challenging background is the internal conversion, shown in Figure 2.3a. A muon decay with an additional virtual photon that converts into an electron-positron pair can be misinterpret as a signal. Since all particles come from the same decay, they are coincident in time and share the same vertex, but they have in average lower momentum and energy due to the two neutrinos carrying away energy which is not detected. The branching fraction can be calculated as a function of missing energy [16] and is plotted in Figure 2.3b. To reach the aimed sensitivity of  $< 10^{-16}$

FIGURE 2.2: Accidental background from three different decays.

at 90% C.L., the invariant mass resolution has to be better than 1 MeV, to be able to reliably distinguish the signal from this background.

FIGURE 2.3: Internal conversion background

#### 2.2.3 Requirements

The characteristics of the decays described above pose stringent requirements on a detector built to search for the signal  $\mu^+ \to e^+e^-e^+$ : First of all, high rates have to be handled. Secondly, excellent vertex reconstruction, momentum resolution and timing are needed. Thirdly the detector has to be very thin to reduce effects of multiple scattering without losing sensitivity for charged particles. The geometrical acceptance and the efficiency of the sensors should be as high as possible to reduce the required measurement time.

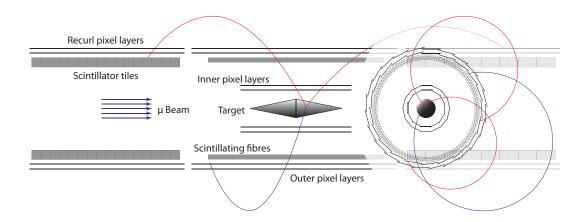

#### 2.2.4 Experimental Concept

The central principle of the Mu3e experiment is to stop more than  $10^{16}$  muons in total on a large surface. Therefore, the muon beam is stopped on a double hollow cone target made of aluminum. The stopped muons decay at rest and the decay particles are bent in a homogeneous static magnetic field of 1 Tesla. Four layers of pixel detectors arranged in two double layers measure the particle tracks with very high precision. Inside the third pixel layer an array of scintillating fibers is used for precise timing. The re-curling electrons and positrons are detected again by a double layer of pixel detectors and stopped in scintillating tiles, which give the most precise timing information of below 100 ps. A sketch of the detector is shown in Figure 2.4.

Due to the low momentum of the decay electrons, the detector is built as thin as possible in order to reduce multiple scattering. In addition, the cooling of the detector is done with a constant flow of gaseous helium [17, 18, 19], which has the advantages of a good heat transfer and low multiple scattering.

Figure 2.4: Schematic view of the Mu3e detector with a  $\mu^+ \to e^+e^-e^+$  signal event decay. On the right side, a view along the beam axis is given. [14]

#### 2.2.5 Sub Detectors

#### **Pixel Detector**

The pixel detector is based on HV-MAPS (see Chapter 3.2) with a pixel size of  $80x80 \ \mu m^2$ . One chip has  $1x2 \ cm^2$  in size in the inner layer and  $2x2 \ cm^2$  in the outer and recurl layers. In total, an area of more than a square meter with 275 million pixels is used to track particles.

To reduce the material budget below 1 % of radiation length per pixel layer, the sensors are thinned to  $50 \mu m$ , glued on top of a  $25 \mu m$  thick Kapton foil and wire bonded to

the Kapton flexprint cables. The readout is supposed to run via serialized 800 MBit/s thin Low Voltage Differential Signaling (LVDS) links and is zero suppressed.

The mechanical structure is self supporting and a mockup has already been constructed with thin glass layers as a silicon sensor replacement. A picture of a half barrel with the two black plastic end pieces and Kapton flexprint cables replacements mounted is shown in Figure 2.5.

Figure 2.5: Kapton pixel support structure prototypes

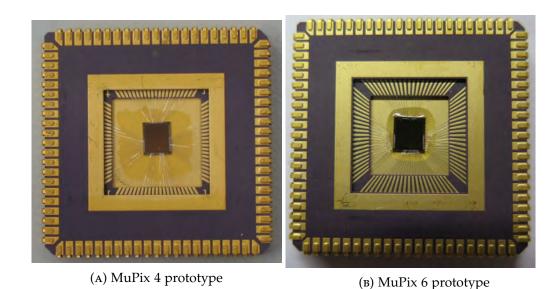

The pixel chip itself is under development and prototypes, shown in Figure 2.6 have been analyzed, tested, characterized and improved in various bachelor and master theses [20, 21, 22, 23, 24]. A detailed description of the prototypes can be found in Chapter 5.

#### Fiber Tracker

The fiber tracker consists of three to five layers of 250 µm diameter and 36 cm scintillating fibers. They are read out by arrays of compact silicon photomultipliers at both ends and have a timing accuracy in the order of a few hundred picoseconds. The fibers are placed at a radius of 6 cm from the target center, in between the inner and outer pixel layers (the grey central area in Figure 2.4). The fiber tracker is developed at

FIGURE 2.6: Top view of the MuPix 4 and 6 prototypes, glued and bonded on a carrier.

the University of Zürich, Eidgenössische Technische Hochschule Zürich, University of Geneva and Paul-Scherrer-Institute.

#### **Scintillating Tiles**

The scintillating tiles consist of  $7.5 \times 7.5 \times 5$  mm sized scintillating tiles, which are read out by silicon photomultipliers as well. The tiles will be placed in the outer recurl layers of the detector (grey blocks in Figure 2.4) and give a very precise timing below 100 ps. They are developed at the Kirchhof-Institut für Physik at Heidelberg [25]. They are also used as a timing reference for the MuPix telescope.

#### 2.2.6 Readout Concept

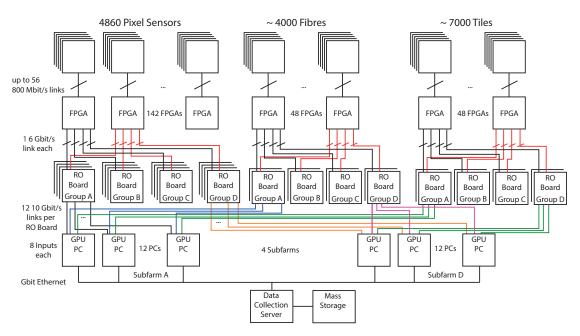

The Mu3e readout chain, sketched in Figure 2.7, is designed to send time slices of the complete detector information to each GPU on the filter farm. Therefore, the complete information from all sub detector systems has to be buffered, sorted, merged and transformed into a useful data structure by the data acquisition (DAQ) system using 238 FPGAs, which are handling a data stream of about 1 TBit/s. This stream is sent to readout boards, which transit short time slices of the complete detector information to the GPU-filter farm. Here, the tracks are reconstructed online, the events of interest are selected and sent to a Data Collection Server. This server writes the data to a mass storage system.

FIGURE 2.7: Schematic of the Mu3e DAQ chain: The data from all sub detectors, sent via 108 links, with 800 MBit/s each, is buffered in 238 FPGAs and sent to the readout boards. From those boards, the data is send to the GPU farm and the tracks are reconstructed. The final data is stored.

#### 2.2.7 Muon Beam

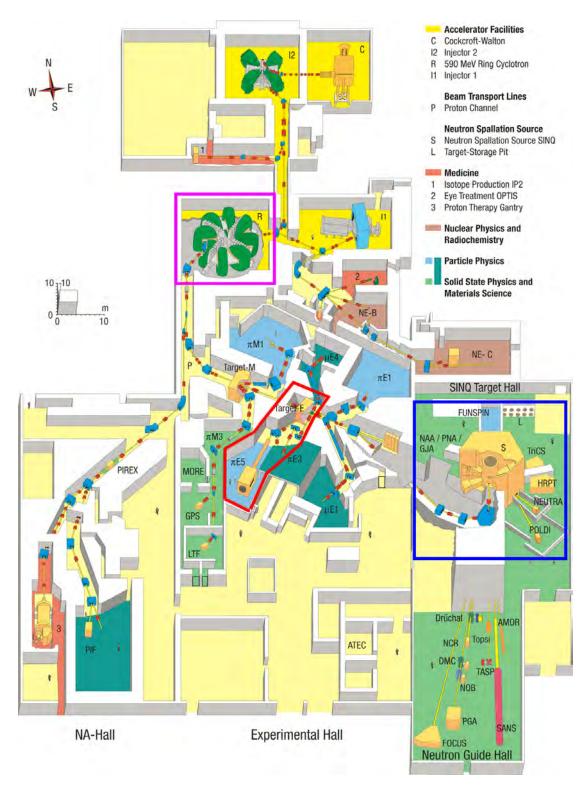

The Mu3e experiment is planned to run in two phases, using the most intense available muon beam at the experimental hall of PSI, shown in Figure 2.8:

The cyclotron at PSI delivers a 2.2 mA 590 MeV proton beam, which hits the rotating carbon target E and produces pions. They decay at rest and the muons are collected into the beamline  $\pi$ E5, which provides a 28 MeV/c muon beam with a rate in the order of  $10^8$  muons per second. This beam and a measurement period of roughly three years are required to reach a sensitivty of  $10^{-15}$ .

Phase II aims for another order of magnitude improvement in sensitivity and therefore needs a more intense muon beam. This could be realized by the planned High intensity Muon Beamline (HiMB) at the SINQ spallation neutron source [26]. This beamline will provide a beam of more than  $3 \cdot 10^9$  muons/s while the Mu3e experiment requires  $2 \cdot 10^9$  stopped muons per second for the aimed sensitivity in Phase II.

FIGURE 2.8: The experimental hall of the PSI with the beamlines and the different areas. The Mu3e experiment will be located in the area surrounded in red. The main accelerator is located at the north-west corner of the hall and marked in purple. The SINQ target is placed on the east side, marked with a blue square. Image from [23] .

## Chapter 3

### Particle Interaction and Detection

In the first part of this chapter the central concepts of particle interactions with matter is discussed. First the interactions of particles are explained, followed by a detailed description of multiple Coulomb scattering.

For particle tracking in general and in the Mu3e experiment, the position of a particle using detector layers of position sensitive devices is measured. They are addressed in a second part, focusing on High-Voltage Monolithic Active Pixel Sensors (HV-MAPS), which are used for the Mu3e experiment and the telescope.

The last part discusses two central tools required to control and readout a detector: Signal transmission and the technology of FPGAs.

#### 3.1 Particle Interactions with Matter

The particle interaction depends strongly on the particle's charge, mass and energy and the matter itself. First of all, one distinguishes between charged and neutral particles. In addition, there is an important difference between light particles (electrons and photons) and heavy particles and ions (protons, neutrons, heavy nuclei,...). In the following, only interactions of electromagnetic charged particles are described, because they are the most relevant for telescopes.

#### **Heavy Particles**

Heavy particles can interact via electromagnetic interaction. The most important one is ionization, which depends strongly on the particle's energy. The mean energy loss is described by the so called Bethe-Bloch formula [27]:

$$-\left\langle \frac{\mathrm{d}E}{\mathrm{d}x}\right\rangle = \frac{4\pi n z^2}{m_{\mathrm{e}}c^2\beta^2} \cdot \left(\frac{e^2}{4\pi\epsilon_0}\right)^2 \cdot \left[\ln\left(\frac{2m_{\mathrm{e}}c^2\beta^2}{I\cdot(1-\beta^2)}\right) - \beta^2\right] \tag{3.1}$$

with the relative velocity  $\beta$  defined as the particles velocity v over the speed of light c, the charge number z, particles energy E, traveled distance x, electron charge e, electron mass  $m_e$ , electron density in the material n and the mean excitation potential  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ , with atomic number  $I \approx 10eV \cdot Z$ ,

#### **Electrons**

Electron interactions with matter are dominated by two processes [1]: Ionization and Bremsstrahlung. The energy loss due to ionization increases logarithmically with energy, while the loss due to Bremsstrahlung increases linearly with energy. For low momentum particles, ionization is therefore dominant. The higher the energy gets, the stronger becomes the influence of Bremsstrahlung. The energy, where both effects are equal defines the critical Energy. Above this energy, the Bremsstrahlung becomes dominant.

Bremsstrahlung describes electromagnetic radiation due to deceleration of charged particles in the field of a nucleus. The emitted photons can build positron electron pairs if their energy is above  $2 \cdot m_e$  and an electromagnetic shower is initialized.

The energy loss is similar to the one of heavy particles with corrections for the lower mass and the possibility of electron exchange with the shell electrons [28].

#### 3.2 Multiple Coulomb Scattering

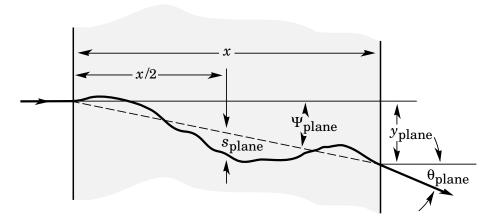

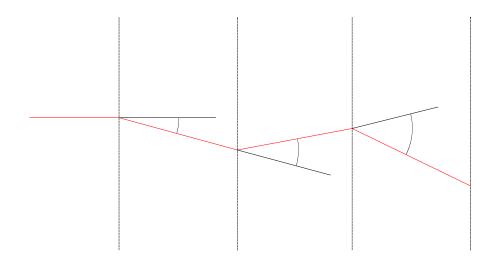

Beside the energy loss particles also scatter at nuclei, while traveling through matter. For precise particle tracking a detailed understanding of multiple Coulomb scattering is required. The theoretical treatment of multiple scattering was studied first in 1922 [29] and fully developed in the 1940ies [30, 31, 32, 33] and summarized in [34]. These theories all assume the scattering angle being independent of the material thickness, which is obviously not correct. Lewis included this effect in his paper from 1950 [35]. The effects, changing the direction of flight and the plane position are summarized for small scattering angles in Figure 3.1. For experimental usage, the Highland [36] parametrisation can be used to define  $\Theta_{MS}$  [37] as

$$\Theta_{MS} = \frac{13.6 \text{ MeV}}{\beta c p} z \sqrt{\frac{x}{X_0}} \left( 1 + 0.038 \ln \frac{x}{X_0} \right),$$

(3.2)

with  $\Theta_{MS}$  being the RMS of the central 98% of the planar scattering angle distribution, the particles velocity in units of the speed of light  $\beta$ , the material's radiation length  $X_0$ , the material's charge number z and the particle's momentum p. Obviously the

FIGURE 3.1: Sketch to visualize the small angle multiple scattering effect [37].

scattering strongly depends on the particle's momentum and becomes more important at lower energies. Therefore the momentum range has to be considered when designing detectors. The displacement of the particle , e.g.  $y_{\rm plane}$  in Figure 3.1, is negligibly small for very thin detectors like the HV-MAPS and only the deflection angle has to be taken into account.

#### 3.3 Particle Tracking Detectors

Particle tracking detectors are used to identify particles, measure the momentum and energy and the velocity. All those concepts require measurements of the particles position on a detector layer. Therefor position sensitive devices are needed.

#### **Position Sensitive Devices**

The detection of particles can only be done via the interaction of particles with some material. A strong interaction of a particle with the detector material allows for high signals, but the particle characteristics change strongly. So there is always a trade-off between detecting a particle and changing its energy and momentum. In the case of a tracking experiment, the momentum and direction of flight should be affected as little as possible. This means, that the multiple Coulomb scattering and energy loss should be small - this only can be achieved by reducing the material budget the particle has to travel through, while it still has to loose enough energy in the detector to be detected. In order to build a position sensitive device, the sensitive medium is usually

segmented and each segment is read out separately. Depending on the task, the active media can be solid, liquid or gaseous and the segmentation size can differ. Besides the common problem of the different velocity of ions and electrons, which are produced by a particle interacting with matter leading to space charge effects, each detection material has advantages and disadvantages:

- **Gaseous:** The main advantage is the small amount of material needed for those devices. A particle traversing the gas leads to ionization. A strong electric field is required to collect the ions and electrons via drift. Gases have the disadvantage of being slow and having a large drift and dead time (*µs*). Additionally there are the issues of aging and strong space charge effects for high rate. Therefore they can only handle low rates and multiplicities.

- Liquid: They are often used to build large volume detectors for neutrino experiments, have the advantage of large volume capacities and have a relatively low spatial resolution. A disadvantage is that thick walls are needed to stand the pressure of the liquid. This makes it not suitable for low momentum tracking. The particles can be detected via created scintillation light, Chrenkov light and drift. For position measurements drift and scintillation can be used. Scintillation and Cherenkov light are fast, but charge collection via drift in those systems (i.e. Time-Projection-Chambers) is very slow.

- Solid: Solid state detectors are the most compact ones and have the advantage of a small absolute size, but usually involve the most expensive technology. They can be very fast, handle high rates and are often used for vertex detection at collider experiments. Their disadvantage is that they have the highest density introducing a large amount of scattering if they are thick (usually in the order of a percent of radiation length).

For a tracking telescope for low momentum particles, one can use gaseous or solid concepts, but if one wants to handle high rates, the best choice is a solid-state detector. Usually, rectangular segmented ones, so called pixel detectors are used. The most common materials are silicon and germanium.

#### 3.3.1 Silicon Pixel Detectors

Silicon pixel detectors are based on a well understood technology and they are used in many experiments (ATLAS, ALICE, CMS,...). The classical approach is to use a sensitive segmented material, which is connected via bump-bonds to a chip with the readout electronics. The charge collection is done in reversed biased HV diodes. The bumps usually consist of a high z material like tin and introduce a significant amount

of multiple scattering. The second and most important issue concerning this hybrid detector type is the huge amount of bumps: It is very complicated to connect all the pixels to their electronics. This makes the technology very expensive. As an example, one can take the ATLAS pixel sensors: They consist of an active part, the p-n-p silicon sensor chip and the separate readout chip. Both elements are connected with 25  $\mu$ m bumps, which are spaced by roughly 50  $\mu$ m. The complete sensor is roughly 1 mm thick and therefore unusable for experiments with low momentum tracking due to the amount of multiple scattering.

The solution for this problem was already developed in the 60s: Active-pixel-sensors (APS). An APS pixel consists of a CMOS-diode as active sensor next to the readout electronics on the same chip. Unfortunately, the sensitive area is only in the order of 30 % of the chip, which is not enough for particle tracking. APS are used for imaging sensors.

#### 3.3.1.1 MAPS

The next step in the active sensor technology development are the Monolithic Active Pixel Sensors (MAPS), which use the complete sensor as active material and implement the electronics directly on top of the active area, as shown in Figure 3.2 [38]. With this technique, one can achieve an active area of nearly 100 % and use the sensors for particle detectors like the STAR experiment [39]. Due to the use of a commercially available CMOS process, the production of these sensors is reasonably priced. Another advantage is, that the minimal structure size for these processes is very small (down to 23 nm). The main disadvantage is the slowness of the sensor, because the charge is collected via diffusion, which is much slower than the collection time in bump bonded sensors, which are operated with HV and have charge collection via drift.

#### 3.3.2 **HV-MAPS**

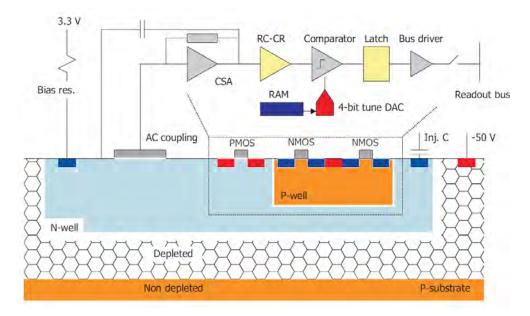

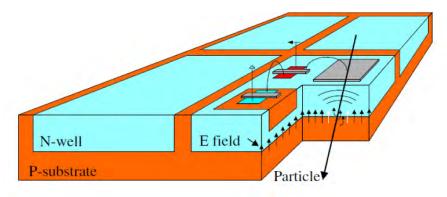

A fast charge collection can be achieved with a novel detector technique, unifying the advantages of the different technologies, the High-Voltage Monolithic Active Pixel Sensors (HV-MAPS) [38]. The principle, shown in Figure 3.2, is to implement the discriminator logic directly in the pixel cell: The p-substrate surrounds a slightly n doped n-well, building up the diode. Applying high-voltage  $\mathcal{O}$  (50–80 V) on this diode in reverse direction results in a small depletion zone of a few  $\mu$ m thickness which is used as a sensitive layer. Charge created in the depletion zone drifts to the electrode in a strong electric field, which leads to a charge collection time below 1 ns. A schematic of a 2x2 matrix of the HV-MAPS is visualized in Figure 3.3. The charge is collected

FIGURE 3.2: Schematic view of a MuPix2 HV-MAPS pixel cell [38]. For the prototypes 4 and 6, the comparator is moved outside the pixel into the periphery.

in the n-well, where the analog and digital electronics are directly implemented. This process is commercially available and reasonably priced.

Figure 3.3: Schematic view of a 2x2 pixel matrix of a HV-MAPS with a charged particle traversing it. The arrows indicate the E field and the charge drift [38].

#### 3.4 Data Transfer and Readout

#### 3.4.1 Field Programmable Gate Arrays (FPGA)

FPGAs started to appear in the 1980s, as a reaction to the growing complexity of electronic circuits. It was not longer sensible to build application-specific integrated circuits (ASICS) for all purposes, due to high costs and development time. In order to keep the advantages of being very fast, compact and having a low power consumption

compared to software solutions, programmable interconnections between different logical elements became more and more important. A good compromise in this context is the use of FPGAs: They consist of an array of up to several thousand basic building blocks which can be interconnected by programmable switches. In principle, each logic cell can be connected to every other cell on the chip and each input or output pad can be connected to every other logic element. A program, written in a hardware description language, can be used to configure the connections and describes the FPGA's functionality.

During the last 30 years, the amount of in- and outputs and logic blocks strongly increased and FPGAs were established as standard components in modern particle physics.

#### 3.4.2 Signal Transmission

#### Digital and Analog Signals

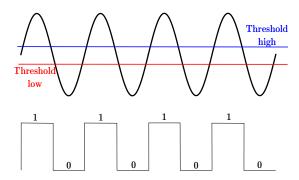

There are two different principles for electrical signal transmission. They can be either analog or digital. Analog signals are continuous signals and are for example represented by the time development of a physical value like the current or voltage. The higher the amplitude of an analog signal, the stronger the corresponding quantity. Those signals have the advantage of transporting the complete information of a system, but they are hard to implement in logic and very sensitive to electrical fluctuations and noise. Therefore, analog signals are usually converted into digital ones. Digital signals take the values one or zero, depending on the intensity of an electrical signal. Under a certain threshold (the red Threshold low line in Figure 3.4), the signal is interpreted as zero, over another threshold it is interpreted as a one (blue Threshold high line in Figure 3.4). This makes for more stable and noise resistant signals. This conversion can be done by so called "Analog-to-Digital-Converters" (ADCs). The simplest ADC is just a comparator, comparing a signal with a threshold. Comparators are also used in the MuPix prototypes to digitize the hit information. There is a large amount of different standards for digital signal transmission. In the following, the ones used in the telescope project are introduced.

#### TTL Signal Standard

The Transistor-to-Transistor-Logic standard describes circuits of transistors and is subdivided into different classes. For the telescope, Low Voltage-TTL (LVTTL) is used. The supply voltage is 3.3 V and the switching threshold is 1.5 V, while the output voltage is 2.4 V.

FIGURE 3.4: Analog to digital conversion

#### **LVDS**

The Low Voltage Differential Signaling (LVDS) is a standard for differential high data rates and the standard is defined by ANSI/TIA/EIA-644-A [40]. The idea is, that a transmitter creates a constant current of 3.5 mA. Depending on the logic level, this current flows from one to the other output and is terminated over a 100  $\Omega$  resistor at the receiver side. Depending on the current direction, this creates a voltage change of  $\pm$  350 mV on the receiver side. The 100  $\Omega$  termination fits the impedance of the transmission line and prevents reflections. In addition, the signal is very robust against cross talk and no net current is flowing, which prevents charging of components.

#### Fast NIM Standard

The Nuclear Instrumentation Standard (NIM) was developed in 1964 for Nuclear and High energy physics and is defined by DOE/ER-0457T [41]. The logic zero is defined as a current of 0 A at 50  $\Omega$ . The logic 1 is defined as a current of -12 to -32 mA corresponding to -0.6 to -1.6 V at 50  $\Omega$  termination.

# Chapter 4

# **Particle Track Reconstruction**

Particle tracks can be reconstructed from particle hits in multiple detector layers. In the following chapter the used coordinate system, the track model and the track fits are described. The first technique is the straight line track assuming no scattering in the detector material which is a good approximation for relatively high particle momenta and therefore low multiple scattering. The main advantage is that this reconstruction method is very fast. A more complex track fit that takes correlations between the planes and the scattering uncertainty into account is explained at the end.

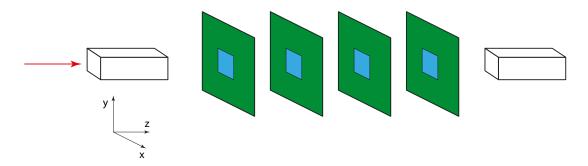

## 4.1 Coordinate System

A Cartesian coordinate system where the z-axis is parallel to the beam is chosen. The x and y axes are defined to be parallel to the columns and rows of the sensors, respectively. It is assumed that the telescope layers do not have any rotations relative to each other.

## 4.2 Track Model

The track model is a simple straight track defined by

$$\vec{x}(z) = \vec{x_0} + \vec{a} \cdot z,\tag{4.1}$$

where  $\vec{x}(z)$  is a two dimensional vector, containing the x and y position as a function of the z position.  $\vec{x_0}$  is the initial track offset and  $\vec{a}$  is a constant two dimensional slope. In a more general matrix form this can be written as [42]

$$Y = \beta X, \tag{4.2}$$

with

$$\beta = (dx/dz, dy/dz, x_0, y_0)^{\mathrm{T}}$$

being the track parameters which have to be estimated and *X* is the propagator of the parameters to the measurement points, which can be represented in the following matrix form:

$$X = \begin{pmatrix} z & 0 & 1 & 0 \\ 0 & z & 0 & 1 \\ \vdots & \vdots & \vdots & \vdots \end{pmatrix} \tag{4.3}$$

$Y = (x_0, y_0, x_1, y_1,...)^T$  are the hits on the telescope. In order to find the best estimate for the parameters, the weighted squared distance from the measurement points has to be minimized:

$$\mathcal{X}^2 = (Y - X\beta)^{\mathrm{T}} \Omega (Y - X\beta) \tag{4.4}$$

$\Omega$  is the weighting matrix, which has to be known.

The terminus  $\mathcal{X}^2$  is usually used to describe the sum of the squared weighted residuals in physics even if this is not the mathematical correct term. Due to multiple scattering effects, which are ignored here, it is not expected that the statistics follow a  $\mathcal{X}^2$  distribution for n degrees of freedom. Therefore it should not be used to estimate the fit uncertainties.

## 4.3 Straight Track Reconstruction without Multiple Scattering

If the effects of multiple scattering are ignored and the tracks are assumed to be perpendicular to the planes, the  $\mathcal{X}^2$  reduces to

$$\mathcal{X}^{2} = \sum_{i=1}^{n} \left( \frac{\left( x_{i} - \left( x_{0} + a_{x} \cdot z_{i} \right) \right)^{2}}{\sigma_{x_{m_{i}}}^{2}} + \frac{\left( y_{i} - \left( y_{0} + a_{y} \cdot z_{i} \right) \right)^{2}}{\sigma_{y_{m_{i}}}^{2}} \right), \tag{4.5}$$

with the measurement uncertainties  $\sigma_{x_{m_i}} = pixel_{x_{length}}/\sqrt{12}$  and  $\sigma_{y_{m_i}} = pixel_{y_{length}}/\sqrt{12}$  at each plane. This is equivalent to  $\Omega = 1$ . To get the best estimators, one can calculate the derivatives of equation 4.5 with respect to the track parameters

$$\frac{\partial \mathcal{X}^{2}}{\partial x_{0}} = \sum_{i=1}^{n} 2 \cdot \frac{x_{i} - (x_{0} + a_{x} \cdot z_{i})}{\sigma_{x_{m_{i}}}^{2}}$$

$$\frac{\partial \mathcal{X}^{2}}{\partial y_{0}} = \sum_{i=1}^{n} 2 \cdot \frac{y_{i} - (y_{0} + a_{y} \cdot z_{i})}{\sigma_{y_{m_{i}}}^{2}}$$

$$\frac{\partial \mathcal{X}^{2}}{\partial a_{x}} = \sum_{i=1}^{n} 2 \cdot z_{i} \cdot \frac{x_{i} - (x_{0} + a_{x} \cdot z_{i})}{\sigma_{x_{m_{i}}}^{2}}$$

$$\frac{\partial \mathcal{X}^{2}}{\partial a_{y}} = \sum_{i=1}^{n} 2 \cdot z_{i} \cdot \frac{y_{i} - (y_{0} + a_{y} \cdot z_{i})}{\sigma_{y_{m_{i}}}^{2}}$$

$$(4.6)$$

and set those equations equal zero. Dividing by the constant pre-factors and rearranging leads to a set of normal equations that can be written in the following matrix form:

$$\begin{pmatrix}

\sum_{i=1}^{n} x_i \\

\sum_{i=1}^{n} (x_i \cdot z_i) \\

\sum_{i=1}^{n} y_i \\

\sum_{i=1}^{n} (y_i \cdot z_i)

\end{pmatrix} = \begin{pmatrix}

\sum_{i=1}^{n} z_i & \sum_{i=1}^{n} 1 & 0 & 0 \\

\sum_{i=1}^{n} z_i^2 & \sum_{i=1}^{n} z_i & 0 & 0 \\

0 & 0 & \sum_{i=1}^{n} z_i & \sum_{i=1}^{n} 1 \\

0 & 0 & \sum_{i=1}^{n} z_i^2 & \sum_{i=1}^{n} z_i

\end{pmatrix} \cdot \begin{pmatrix} a_x \\ x_0 \\ a_y \\ y_0 \end{pmatrix} \tag{4.7}$$

Inverting this matrix (see Appendix A) leads to analytic expressions for the estimated track parameters. Implementing those equations in C++ gives a fast and non iterative algorithm to reconstruct straight tracks at the expense of ignoring possible correlations.

#### **Parameter Uncertainties**

The fit uncertainty of a parameter p is defined over the second derivative of  $\mathcal{X}^2$  [42]:

$$\frac{1}{\delta p^2} = \frac{1}{2} \frac{\partial^2 \mathcal{X}^2}{\partial p^2} \tag{4.8}$$

In the case of equation 4.5 those derivatives can be calculated analytically:

$$\sigma_{a_x}^{-2} = \frac{1}{2} \frac{\partial^2 \mathcal{X}^2}{\partial a_x^2} = \sum_{i=1}^n \frac{z_i^2}{\sigma_{x_i}^2}$$

(4.9)

$$\sigma_{x_0}^{-2} = \frac{1}{2} \frac{\partial^2 \mathcal{X}^2}{\partial x_0^2} = \sum_{i=1}^n \frac{1}{\sigma_{x_i}^2}$$

(4.10)

$$\sigma_{a_y}^{-2} = \frac{1}{2} \frac{\partial^2 \mathcal{X}^2}{\partial a_y^2} = \sum_{i=1}^n \frac{z_i^2}{\sigma_{y_i}^2}$$

(4.11)

$$\sigma_{y_0}^{-2} = \frac{1}{2} \frac{\partial^2 \mathcal{X}^2}{\partial y_0^2} = \sum_{i=1}^n \frac{1}{\sigma_{y_i}^2}$$

(4.12)

## 4.4 Straight Track Reconstruction with Correlations

The second implementation (implemented by M. Kiehn [43]) is again based on the straight track model, but also takes correlations between neighboring planes and multiple scattering into account. Starting from a reference plane one can propagate the uncertainties to the other layers. Therefore, the weighting matrix  $\Omega$  is more complex:

$$\Omega = \begin{pmatrix}

\cos_m(0) & 0 & \dots & 0 \\

0 & \cos_m(1) & 0 & \vdots \\

\vdots & 0 & \ddots & 0 \\

0 & 0 & 0 & \cos_m(n)

\end{pmatrix}$$

(4.13)

In the above matrix, the  $cov_m(i)$  are the 2x2 uncertainty matrices at each plane, which are the sum of the propagated multiple scattering uncertainty and the local measurement uncertainty (for more details see Appendix A).

Minimizing the  $\mathcal{X}^2$  can again be done by calculating the derivatives of  $\mathcal{X}^2$  and setting them equal to zero [42]. This leads to the solution

$$\beta = (X^{T} \Omega^{-1} X)^{-1} X^{T} \Omega^{-1} Y, \tag{4.14}$$

which can be solved numerically. This needs more computational effort due to numerical matrix inversion and the iterative calculation the local measurement covariance matrices.

# Part II Setup & Measurements

# Chapter 5

# The MuPix Telescope

The MuPix telescope is discussed in this chapter in detail. The first part motivates the development and compares the telescope with existing ones. This is followed by an overview over the telescope concept. The components are introduced in the following starting with the mechanical setup. Subsequently the MuPix sensor is explained. The last part addresses the used electronics, focusing on a description of the customized PCBs.

## 5.1 Motivation

Particle tracking telescopes are developed as a tool for track reconstruction, especially at testbeam facilities and used to test the position and time resolution of detector prototypes. The two most actively used telescopes in Europe are the TimePix telescope at SPS at CERN and the EUDET telescope at DESY II at DESY. Both are individually customized for local beam properties. A comparison between those telescopes and the MuPix telescope is shown in Table 5.1.

The Timepix telescope uses bump bonded sensors and is therefore thick, while the MuPix and the EUDET telescope consist of MAPS, which are very thin but slow. The pixel sensor size varies from 18.4  $\mu$ m for the EUDET to 80  $\mu$ m for the MuPix telescope, resulting in a pointing resolution from 1.8  $\mu$ m to 12  $\mu$ m for 180 GeV pions. For low momentum particles, like 50 MeV electrons, the pointing resolution is 150  $\mu$ m for the MuPix telescope, which is more precise than the others assuming 1 cm flight distance and dominating multiple scattering effects. The main advantage of the MuPix telescope is the high track rate of 20 MHz, which it is designed for.

The TimePix fits best the requirements of the beam at SPS and the EUDET for DESY II. For the high rate and low momentum beam at PSI, no customized pixel telescope exists. This is the reason why the MuPix telescope project was started.

|                         | Timepix Telescope       | EUDET Telescope           | HV-MAPS Telescope        |

|-------------------------|-------------------------|---------------------------|--------------------------|

| Pixel size              | 55 μm                   | 184 μm                    | 80 μm                    |

| Pointing resolution     |                         |                           |                          |

| 180 GeV $\pi$           | 2 μm                    | 18 μm                     | 12 μm                    |

| 50 MeV e <sup>-</sup> * | 400 μm                  | 180 µm                    | 150 μm                   |

| Material                | 300 µm sensor           | 50 μm sensor              | 50 μm sensor             |

|                         | 700 µm readout          | 50 µm foil                | 25 µm Kapton             |

| in radiation length     | 28 ‰                    | 0.7 ‰                     | 0.6 ‰                    |

| Time resolution         | 1 ns (in special plane) | 1125 μm                   | 17 ns                    |

|                         | 16 ms otherwise         |                           |                          |

| Frame rate              | 60 Hz                   | 9 kHz                     | 20 MHz                   |

| Maximum track rate      | 15.5 kHz                | $\approx 100 \text{ kHz}$ | $\approx 20 \text{ MHz}$ |

| Track reconstruction    | mostly offline          | offline                   | online                   |

Table 5.1: Comparison of the MuPix, Timepix and EUDET telescopes. The MuPix telescope is named HV-MAPS Telescope [44].

Another argument to build the telescope is to perform an integration test: The Mu3e experiment has a streaming readout providing absolute time information for all hits. Up to 2013, only single sensor standalone tests for the pixel sensors have been carried out. To scale up the system to a telescope with four planes is a perfect step towards a larger detector system.

## 5.2 Telescope Concept

The central idea of a particle tracking telescope is to detect the particle in multiple detector planes and reconstruct its track while minimizing the impact on the particle's track. The MuPix telescope is designed to track low momentum particles, where multiple Coulomb scattering is the dominating effect (compare Chapter 3.1) for the track resolution. Therefore the layers should be as thin as possible and only medium sized pixels are needed. The telescope consists of four layers of MuPix prototypes. An optional "device under test" (DUT) could be placed in the middle, but was neither used nor implemented in this thesis.

Figure 5.1 shows the four sensors layers, framed by two optional trigger scintillators, which can be used as a timing reference for the telescope.

The MuPix chips, thinable down to  $50 \, \mu m$  are used as sensors. The sensors used in the measurements described in this thesis are between  $250 \, \text{and} \, 300 \, \mu m$  thick. They are mounted either on a carrier (for the DESY T22 test beam, see Chapter 8), directly glued to a thinned PCB board (for the PSI test beam, see chapter 9) or glued on Kapton,

<sup>\*</sup>Assuming 1 cm flight distance and dominating multiple scattering effects.

FIGURE 5.1: Design concept of the MuPix Telescope: In white, the two trigger scintillators are shown, framing the blue drawn MuPix chips, mounted on MuPix-PCBs drawn in green.

mounted on a perforated PCB. This results in a radiation length of 30 % per layer for the chip on carrier and 2.5 % for the chip on a thin board, respectively.

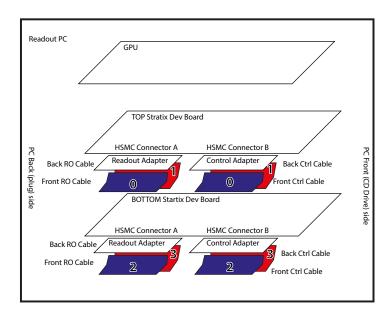

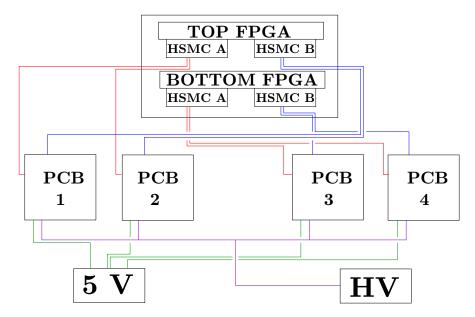

To readout the telescope a powerful computer, housing two Stratix IV FPGA development boards with one FPGA each, inserted in the PCIexpress ports of the mainboard and an Intel i7 Central Processing Unit ("CPU") is used. It also contains an NVIDIA GForce Graphic Processing Unit ("GPU") and 16 GB Double Data Rate 3 Synchronous Dynamic Random Access Memory ("DDR3-SDRAM"). A 256 GB Solide State Drive ("SSD") is used for operating system usage and 3x3 TB Hard Disk Drives ("HDD") serve as data storage volume.

## Nomenclature

The connections of the test PCBs to the computer are organized as shown in Figure 5.2: The FPGA card mounted in the top PCIe slot is called TOP StratixDEVBoard, the lower one BOTTOM StratixDEVBoard. The High Speed Mezzanine Card (HSMC) connectors A are used for readout and the connectors B for slow control. Each HSMC adapter card has two 40 line ribbon cable connectors, one at the back, called BACK and one at the front, called FRONT.

FIGURE 5.2: Scheme of the telescope PC side readout and control electronics.

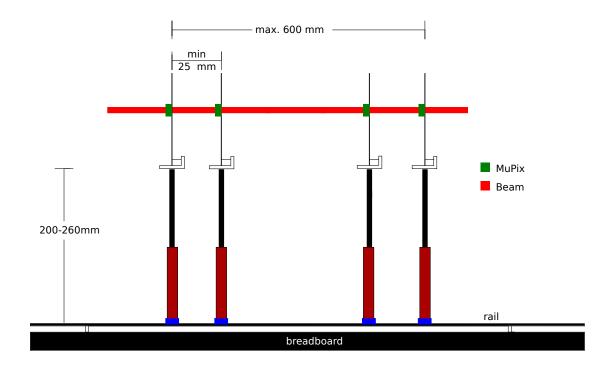

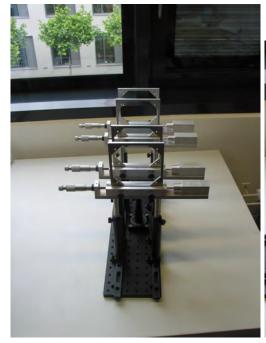

## 5.3 Mechanics

The telescope is designed to be as stable and compact as possible. To realize this concept with maximal flexibility, optomechanical parts from Thorlabs are used for all components, except for the PCB holders which are self designed and constructed by the institute's workshop. The use of commercially available parts has the advantages of being cheap and easily replaceable in the case of mechanical failure, damage or activation after a testbeam. The system is placed on two parallel, 10 cm spaced, optical rails mounted on an optical breadboard with a size of 60x15 cm<sup>2</sup> as shown in Figure 5.3. Each sensor is mounted on a PCB holder which is connected to two stainless steel posts, which have the same spacing as the rails. Those posts are plugged into post holders, standing on rail clamps, which are connected to the rails and can be fixed via a screw. Due to this structure, the layers can be moved independently of each other on the rails. The second advantage of the use of two rails is, that the sensors can not be rotated relative to each other.

The minimal distance between two layers is given by the sum of the thickness of the thickest component on the MuPix boards on both sides and the PCB itself. In the current design, this leads to a minimal spacing of 2.5 cm between two layers. The minimal distance between two double layers, spaced 2.5 cm is roughly 8 cm in the

Figure 5.3: Overview over the mechanical structure of the telescope: The system is placed on an optical breadboard and the MuPix sensors are mounted on stainless steel posts, placed in post holders, colorord dark red. The postholders are mounted on a optical rail via rail clamps, drawn in blue, for maximal flexibility.

current setup. This is a result of the black fixation screws shown in Figure 5.4. To reach the minimal spacing, the screws have to point into opposite directions. This results in two screws touching each other, if two double planes are moved closely together.

A simple structure consisting of two posts and two cross studs are used as a stress relief for the readout and slow control ribbon cables. In principle the system can be extended by adding another breadboard and two rails, for larger DUTs or additional pixel layers.

## 5.3.1 PCB Holders

The PCB holders are the only non commercial parts and were built in house to fit the custom PCBs. Three different prototypes all consisting mainly of aluminum have been developed:

The first prototype was designed to mount the PCB on only one single post (see Figure 5.5a and 5.5b bottom). This prototype has the advantage of being mountable on a rotational stage, but the disadvantage of being unstable. It is not possible to fix the planes reliably. They are also unstable and start vibrating if the environment is vibrating. It is also complicated to align two of those holders without any rotation relative to each

FIGURE 5.4: Front and side view of the MuPix telescope mechanics. The 60x15 cm<sup>2</sup> breadboard carries the two parallel optical rails, where the post holders are mounted on. The silver parts are the stainless steel post holders and the PCB holder version 3.

#### other.

Therefore, a second prototype (see Figure 5.5a and 5.5b top), similar to the first one, but mounted on two posts was designed. This prototype version improves the stability and is easier to align and was used at the DESY February 2014 test beam. However it has the disadvantage of not being movable horizontal to the beam, while the vertical direction can be adjusted by moving the posts in the holder up or down. The vertical alignments turned out to be very precise.

The problem of horizontal movement is solved by placing the PCB holder on an adjustable stage and is realized in the third prototype, which is also mounted on two steel posts and shown in Figure 5.5c. The position of the sensor can be adjusted with a micrometer screw, moving the PCB. A spring, placed in the aluminum cylincder on the right of Figure 5.5c provides the necessary back pressure. Screws vertical to the PCBs can be used to fix the setup. It is designed symmetrically to keep the center of mass between the two posts and not introduce any rotational tension in the mechanics. The second advantage is that the guide rail for the PCB frame can be turned around, which also moves the fixation screws to the other side. This makes it possible to deal with tight space constraints and gives the opportunity to move two planes very close together.

The aluminum plate carrying the components of PCB holder version 3 has a thickness of 2.5 cm. The total thickness, including the screws, is 4.2 cm. This could be reduced by a factor of two if needed.

(A) Side view of the first prototypes: foreground is version 1 and background version 2.

(B) Top view of the first prototypes: Bottom is version 1 and top version 2.

(c) The third prototype with a MuPix test board and a MuPix4 chip glued on board. The micrometer screw on the bottom left is used to move the test board with a precision of 1  $\mu$ m. The spring, inside an aluminum cylinder on the right side is used to create back pressure.

FIGURE 5.5: The three generations of PCB holder prototypes.

## 5.4 MuPix Prototypes

The Mu3e pixel sensor is currently under development. During this thesis, two prototypes, the MuPix4 and the MuPix6 were used as sensors for the telescope; their properties are compared in Table 5.2. Both have a fully digital readout mode, including a column and row address as well as a time information, the time stamp.

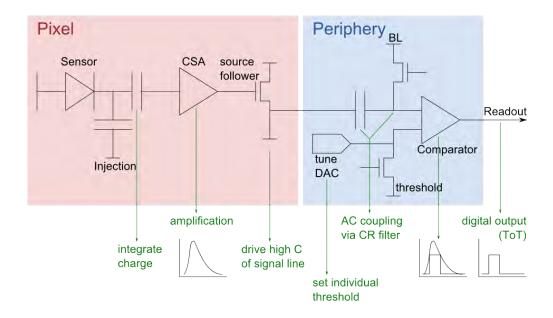

## **5.4.1** Sensor Electronics

The two prototypes have similar electronics, which are sketched in Figure 5.6. Each pixel has electronics, placed directly on the sensor:

The sensor itself is a diode. The charge deposited by a particle is integrated on capacitor

| MuPix | Columns | Rows | Pixel | Pixel  | area               | active             | amplifier    |

|-------|---------|------|-------|--------|--------------------|--------------------|--------------|

|       |         |      | width | height |                    | area               |              |

|       |         |      | [µm]  | [µm]   | [mm <sup>2</sup> ] | [mm <sup>2</sup> ] |              |

| 4     | 32      | 40   | 92    | 80     | 14.72              | 9.22               | single stage |

| 6     | 32      | 40   | 103   | 80     | 16.18              | 10.55              | double stage |

TABLE 5.2: The MuPix prototypes used for the telescope.

and amplified by a charge sensitive amplifier (CSA). The amplified analog signal is sent via a source follower, that drives the high capacity of the signal line to the periphery. For the MuPix6 prototype a second amplification stage is located in the periphery. For both prototypes the signal is AC coupled via a CR filter to the baseline. This is done to decouple the charge signal from the other currents on the chip. At this point, the signal is also shaped [24]. A comparator compares now the voltage to a threshold. If it is above this threshold a digital output is created for the MuPix4. The MuPix6 signal is inverted in the second stage. Therefore the signal has to be below a certain threshold to create a digital output signal.

A tune DAC, which can be set for each pixel individually can be used to adjust the

FIGURE 5.6: Schematic for signal generation on the MuPix prototypes [45].

threshold of each pixel to compensate for fluctuations in the baseline between different pixel.

In the pixel electronics an additional capacitor can be used to send a charge signal onto the pixel imitating the charge deposition by a particle. This is the injection signal and can be used to test and characterize the prototypes. For the MuPix prototypes, there are two different injections available, injection 1 and 2, which simulate particle hits in all even and odd double rows.

To adjust the performance of the prototypes it is possible to change the amplification of the CSAs, the driving force of the source follower and the signal shaping. This can be done by the use of digital to analog converters (DACs), which control the bias currents of the chip. The global threshold can also be set externally. Setting these DACs to appropriate values is crucial for the chip performance. A detailed study of the influences of those DACs for the MuPix4 is performed by a comparison of simulation and measurement [23, 46]. A list of the DAC settings used for the two sensors can be found in Appendix E.

## 5.4.2 Hit Storage

The digital output created by the comparator is sent to the next part of the digital electronics, where the hit information is created. Each pixel has its own readout cell in the digital part of the sensor, where the time stamp of each hit can be stored. For the MuPix4 and 6, this time stamp has 8 bits and has to be provided externally. If the comparator sends a signal, the time stamp is latched and stored. The latching of the time stamp is asynchronous to the switching frequency of the counter applied from the outside. Therefore it can happen, that the signals are switching while they are latched. This can result in wrong time information.

As long as the pixel is not read out, the pixel can not store additional hits and is blind until it is read out.

## **Gray Code**

To prevent wrong time information, one can encode the counter, such that only one bit is switching at a time. This is the principle of the Gray Counter [47] and results in a reliable time information. In the worst case, the latched time is of by one in this case. One possible Gray Counter is the so called reflected binary code, which is chosen for the telescope project. One possible C++ implementation can be found in Appendix B.

## 5.4.3 MuPix Readout

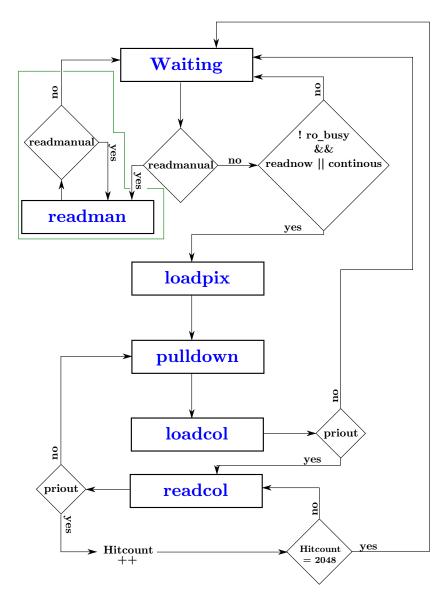

The prototypes MuPix 4 and 6 need to be read out and controlled externally. This is done by an FPGA, which also sends the time information to the sensor. The firmware [44] includes a state machine, which performs the readout of the sensor. This state machine is shown in Figure 5.7 and works as follows: The FPGA's initial state is a wait state, that checks for the readmanual signal which is on if the readout sequence is sent

FIGURE 5.7: The FPGA state machine for the MuPix readout. The manual readout mode (framed green) is not used for performance runs, only for debugging.

in fixed time intervals set by the user. This readout mode is only used for debugging and is switched off for data taking. If the readmanual signal is off, the automatic readout mode is used. In this case the ro\_ busy bit, indicating whether the FPGA is busy with other things, the readnow and the continuous readout signals are checked. If the ro\_ busy signal is off and one of the others is on, a readout sequence is initialized: First, the loadpix signal is sent to the MuPix, that copies the hit information into the readout part of the digital logic. At this point the pixel itself is reset and sensitive again. In the next step a pulldown signal is emitted to initialize the readout bus. Now the loadcol signal is sent and the MuPix is loading the first hit from each logical column into the bus. If at least one hit is copied to the bus, the priout signal is emitted by the chip. If no hits are copied, the FPGA returns to the wait state. As long as the priout

signal stays on, the FPGA sends readcol signals and one hit from the bus is sent to the FPGA. If the priout turns off, the FPGA goes to the pulldown state again. This procedure continues until all hits are read out, meaning the priout stays off or a number of 2048 hits (roughly twice the amount of pixels and named Hitcount in Figure 5.7) is read out. The FPGA writes the hit information in hit blocks into its local memory.

## 5.4.4 Special Characteristics of the Prototypes

The MuPix 4 has two main issues concerning the performance: First the row address of each odd double column is reset before it is read out. This effect is understood and removed in the MuPix 6 prototype. The second issue concerns the time stamps. Due to digital cross talk it is impossible to activate the time stamps in our test setup. In another setup the time stamps of the MuPix 4 are working. So this is introduced by the setup itself. This issue is also solved for the MuPix 6 prototype tests.

## 5.5 Electronics and Cabling